Imperial College London Department of Computing

## Accelerating Optimisation-Based Anisotropic Mesh Adaptation using nVIDIA's CUDA Architecture

Georgios Rokos

Submitted in part fulfilment of the requirements for the MSc Degree in Computing Architecture of Imperial College London, September 2010

#### Abstract

This report presents the design and implementation of 2D anisotropic mesh adaptivity on nVIDIA's CUDA architecture. Mesh smoothing is a component of anisotropic mesh adaptivity, a numerical technology of some importance in Computational Fluid Dynamics (CFD). Adapting the size and shape of elements in an unstructured mesh to a specification encoded in a metric tensor field is done by relocating mesh vertices using an optimisation algorithm, like the one proposed by Pain et al. in 2001. This computationally heavy task can be accelerated by engaging nVIDIA's CUDA, a massively parallel and floating-point capable architecture. In order to ensure correct parallel execution, we implemented the parallel framework based on the use of independent sets proposed by Freitag et al. in 1998.

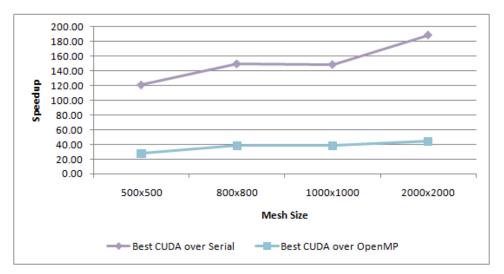

The report contains all related algorithms and architectural details, gives design and implementation descriptions and lists various CUDA code optimisations which can lead to a speedup of up to 190 times over the serial CPU code and up to 45 times over an eight-threaded OpenMP code. Performance analysis shows that CUDA's texture memory can assist in accelerating execution by 2.5 times and that high register usage is the main limiting factor for better performance. The report closes with a short comparison between CUDA and the older Cell Broadband Engine Architecture, explaining why programming in CUDA is easier and expected to yield better performance results.

#### Acknowledgements

I would like to express my gratefulness and thank following people for their contribution to the accomplishment of this project:

- Professor Paul Kelly, who took the initiative, proposed this project and accepted to take me under his supervision, giving me the chance and all necessary lab equipment to build *CUDAMesh64* and fulfil the requirements for my MSc degree.

- Dr Gerard Gorman, who supported me throughout this project, giving me invaluable advice and guidance, providing all necessary algorithmic knowledge and assuming the role of the second supervisor, devoting a great amount of his time.

- Graham Markall, who assisted me in the technical part of the project, having interesting discussions with me on nVIDIA's CUDA, an architecture with which I had no previous experience, and providing lab support.

- My family who should ered the financial requirements of my MSc course and provided emotional support against all difficulties of living a broad for the first time in my life.

'I do not think there is any thrill that can go through the human heart like that felt by the inventor as he sees some creation of the brain unfolding to success... Such emotions make a man forget food, sleep, friends, love, everything.'

$Nikola \ Tesla$

# Contents

| A | bstra | $\mathbf{ct}$                                       | i   |

|---|-------|-----------------------------------------------------|-----|

| A | cknov | wledgements                                         | iii |

| 1 | Intr  | oduction                                            | 1   |

|   | 1.1   | Motivation and Objectives                           | 1   |

|   | 1.2   | Related Work                                        | 2   |

|   | 1.3   | CUDA and CFD                                        | 2   |

|   | 1.4   | Contributions                                       | 2   |

|   | 1.5   | Statement of Originality                            | 3   |

|   | 1.6   | Report Outline                                      | 3   |

| 2 | Bac   | kground Theory                                      | 5   |

|   | 2.1   | Anisotropic Mesh Adaptivity                         | 5   |

|   |       | 2.1.1 Partial Differential Equations and Meshes     | 5   |

|   |       | 2.1.2 Objective Functionals: Element Size and Shape | 6   |

|   |       | 2.1.3 Anisotropic PDEs                              | 7   |

|   |       | 2.1.4 Metric Tensors                                | 7   |

|   |       | 2.1.5 Vertex Smoothing                              | 9   |

|   |       | 2.1.6 Laplacian Smoothing                           | 10  |

|   |                | 2.1.7 Algorithm by Freitag et al              | 11 |

|---|----------------|-----------------------------------------------|----|

|   |                | 2.1.8 Algorithm by Pain et al                 | 13 |

|   |                | 2.1.9 Rescaling the metric tensor             | 15 |

|   | 2.2            | Parallel Execution                            | 16 |

|   |                | 2.2.1 Operation Task Graph                    | 17 |

|   |                | 2.2.2 Vertex Smoothing Elemental Operation    | 17 |

| 3 | nVI            | DIA's CUDA Architecture                       | 19 |

|   | 3.1            | Architectural Overview                        | 20 |

|   |                | 3.1.1 Memory Model                            | 21 |

|   |                | 3.1.2 Programming Model                       | 24 |

|   |                | 3.1.3 Execution Model                         | 25 |

|   | 3.2            | Code Optimisations                            | 25 |

|   |                | 3.2.1 Memory Optimisations                    | 25 |

|   |                | 3.2.2 Execution Configuration Optimisations   | 26 |

|   | 3.3            | C++ support                                   | 26 |

| 4 | $\mathbf{Des}$ | ign and Implementation                        | 29 |

|   | 4.1            | Design choices                                | 29 |

|   | 4.2            | Meshes and the VTK framework                  | 30 |

|   | 4.3            | The object-oriented model and data structures | 31 |

|   |                | 4.3.1 MeshOptimizer class                     | 31 |

|   |                | 4.3.2 Mesh class                              | 31 |

|   |                | 4.3.3 Vector2d structure                      | 32 |

|   |                | 4.3.4 Vector2dPair structure                  | 32 |

|   |     | 4.3.5   | Vertex class                                            | 32 |

|---|-----|---------|---------------------------------------------------------|----|

|   |     | 4.3.6   | Element class                                           | 32 |

|   |     | 4.3.7   | Cavity class                                            | 33 |

|   |     | 4.3.8   | Metric class                                            | 33 |

|   |     | 4.3.9   | ObjectiveFunctional class                               | 34 |

|   |     | 4.3.10  | OptimizationAlgorithm namespace                         | 35 |

|   | 4.4 | Paralle | el implementation                                       | 36 |

|   |     | 4.4.1   | IndependentSets class                                   | 36 |

|   |     | 4.4.2   | GraphColoring namespace                                 | 36 |

|   |     | 4.4.3   | Parallel execution using OpenMP and CUDA                | 36 |

|   | 4.5 | Optim   | isation techniques                                      | 38 |

|   |     | 4.5.1   | Treating the metric tensor field as graphics texture    | 38 |

|   |     | 4.5.2   | Putting boundary vertices in dedicated independent sets | 39 |

|   |     | 4.5.3   | Stripping Cavity objects off Element information        | 39 |

|   |     | 4.5.4   | Using on-chip memory primarily as L1 cache              | 40 |

|   | 4.6 | Impler  | nentation difficulties                                  | 40 |

|   |     | 4.6.1   | Automatic Differentiation                               | 41 |

|   |     | 4.6.2   | CUDA linker                                             | 41 |

|   |     | 4.6.3   | METIS and two-level graph colouring                     | 41 |

| 5 | Exp | erime   | ntal results and evaluation                             | 43 |

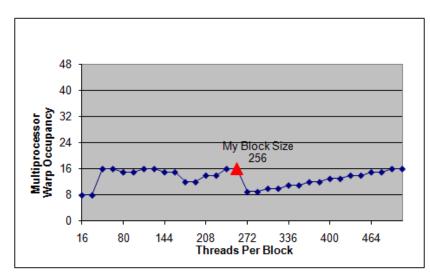

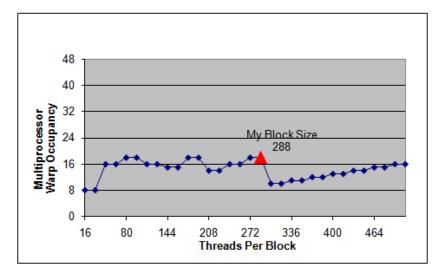

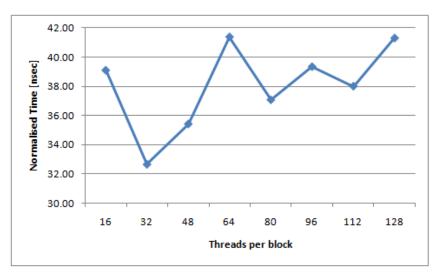

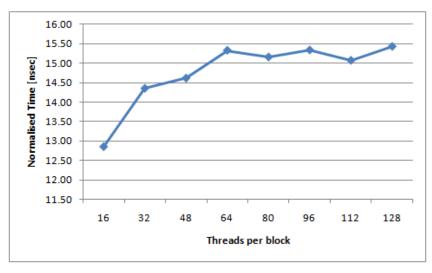

|   | 5.1 | Execut  | tion Configuration                                      | 43 |

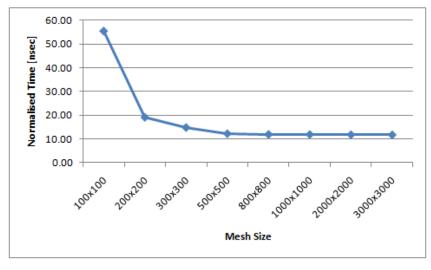

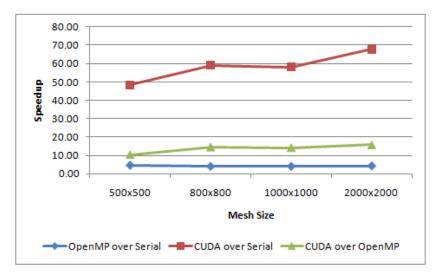

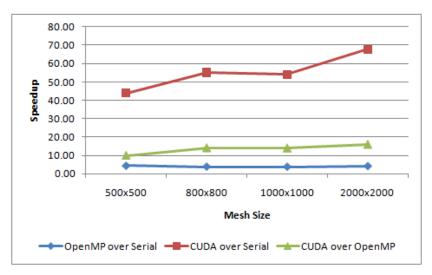

|   | 5.2 | Scaling | g with different mesh sizes                             | 45 |

|   | 5.3 | Basic   | CUDA version speedup                                    | 45 |

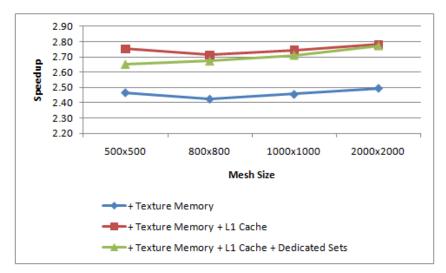

|   | 5.4 | Optim   | isations                                                | 48 |

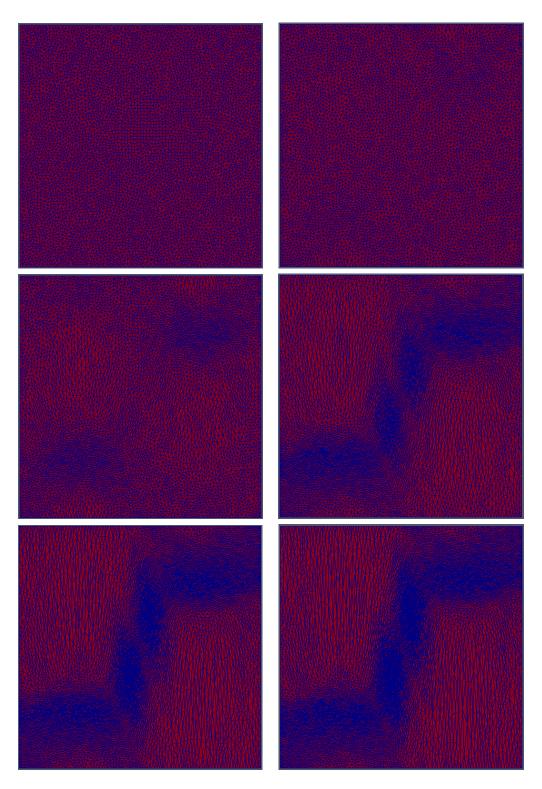

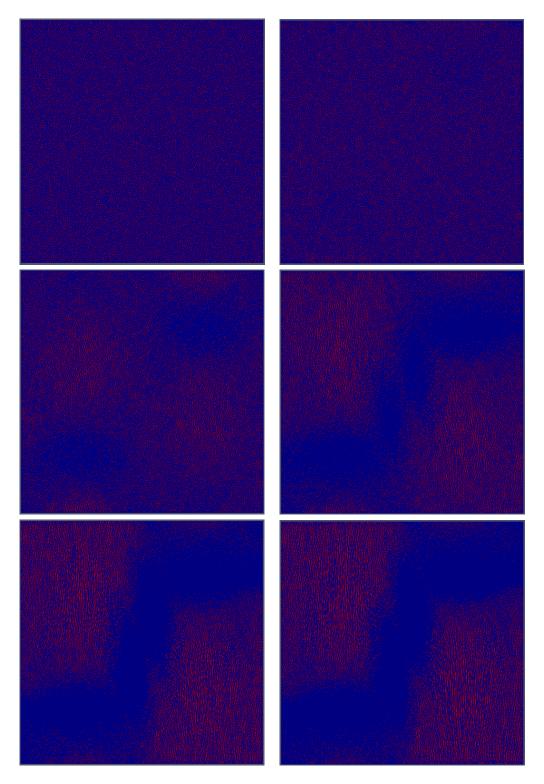

|    | 5.5   | Comp   | exity of the Anisotropic Mesh Adaptivity problem | 51 |

|----|-------|--------|--------------------------------------------------|----|

| 6  | Con   | clusio | ns and future work                               | 55 |

|    | 6.1   | Conclu | nsions                                           | 55 |

|    |       | 6.1.1  | CUDAMesh64                                       | 55 |

|    |       | 6.1.2  | nVIDIA's CUDA vs IBM's CBEA                      | 56 |

|    | 6.2   | Future | Work                                             | 58 |

| Bi | bliog | graphy |                                                  | 58 |

## Chapter 1

# Introduction

Mesh adaptivity is an important numerical technology in *Computational Fluid Dynamics* (CFD). CFD problems are solved numerically using unstructured meshes, which essentially represent the discrete form of the problem. In order for this representation to be accurate and efficient, meshes have to be adapted according to some kind of error estimation. Furthermore, this error estimation may also encode information about a possible special orientation of the problem under consideration, in which case we say that the underlying dynamics is anisotropic.

Various techniques and algorithms can be used to adapt a mesh. One sophisticated technique, which is considered to yield very good results, is the optimisation-based vertex smoothing [FJP95]. It can be implemented using a great variety of algorithms, each one having its own computational advantages and disadvantages over the others, therefore being more or less suitable for a given computer architecture. In this project we only investigated two-dimensional cases, although a large part of the algorithmic background and codebase could be used and extended to three-dimensional problems.

## 1.1 Motivation and Objectives

Adapting a mesh to an error estimation involves an enormous amount of floating-point operations which can push even the most powerful processing units to their limits. Modern trends like nVIDIA's CUDA and ATI's Stream architectures have made the tremendous floating-point processing capabilities of GPUs available to a wide range of applications apart from their traditional usage in games, graphics and motion picture processing. This shift in GPU target applications has been very successful so far and we are already speaking of supercomputers consisting of graphics processors. Moreover, there is a dormant tendency in CPU industry to slowly integrate the two traditional processing worlds: general purpose (CPU) and massive floating-point (GPU) computing. There are already some early attempts towards this direction, like IBM's Cell Broadband Engine Architecture.

The CUDA platform offers great computational power at relatively low cost (in terms of space occupied, power consumption during operation and money spend to acquire the essential hardware). These properties make it a perfect candidate for accelerating mesh adaptation software. The purpose of this project is writing a new application framework which implements various optimisation-based vertex smoothing algorithms along with the proposal by [FJP98] for their parallel execution, enabling mesh adaptation to be accelerated on CUDA GPUs. It is interesting to perform a comparison between this new platform and conventional hardware and see how well CUDA can compete against the old trends in terms of performance and scalability.

## 1.2 Related Work

During the past years, the Applied Modelling and Computation Group at Imperial College London has developed a CFD code called "Fluidity". Fluidity is a general-purpose numerical solver for fluid dynamics problems which uses the finite element methods with unstructured finite element meshes. So far it has been used in a wide variety of problems such as heat transfer, oceanic flow and other complex, compute-intensive applications. It was designed to run on conventional hardware and take advantage of distributed memory parallel computers using the *Message Passing Interface* (MPI) [ML09]. Complexity of modern CFD applications, however, shows that calculations are expensive; using conventional hardware requires thousands of processors and many days of processing.

Taking this into account, it becomes obvious that it would be useful to the modelling community to have an extensible, CUDA-enabled framework so that the group can actually take advantage of modern, high-performance GPUs in their modelling and simulation tasks. This framework is built with extensibility in mind so that new adaptation algorithms can be easily incorporated in the future.

## 1.3 CUDA and CFD

CUDA has already been used to create solvers for computational fluid dynamics problems. Relevant works include [GBT06], which was an attempt to enable CUDA capabilities in an existing application (much like the case of Fluidity), [TccS09], which constitutes an exploration into solving the Navier–Stokes equation on desktop systems using single, dual and quad GPU configurations and [ELD08], which addresses the simulation of a hypersonic vehicle configuration.

In all cases, execution performance was impressive compared to conventional architectures. [TccS09] managed to get a speedup of 100 times using a Quad Tesla S870 server, compared to serial CPU code running on an AMD Opteron 8216. A key point in application performance, which also scales well as the number of GPUs increases, proved to be the extensive usage of shared memory. [GBT06] report that CUDA computing does not perform very well on small problems because the whole overhead of engaging the GPU outweighs the few benefits obtained by low-level parallelism. Additionally, if CPU is assigned with global reduction tasks like result accumulation or data updates there is a great amount of time when GPUs remain idle. Another important conclusion coming from this work is that the single-precision restriction on floating-point arithmetic does not seem to affect result accuracy (in this project, though, we work on *Fermi* chipsets which are proportionally powerful in double-precision arithmetic). [ELD08] have derived some interesting results by analysing their application's performance model. They propose using texture memory to merge small data blocks into one large group so that computational load is kept high at all times and use shared memory with the purpose of increasing memory bandwidth for stencil operations.

### 1.4 Contributions

The venture of accelerating the optimisation-based anisotropic mesh adaptation on CUDA has led to the following contributions:

- This is the first adaptive mesh algorithm implemented on CUDA as far as the author is aware.

- A speedup of 190 times was achieved over a conventional CPU, which is relatively high compared to other codes.

• Using texture memory to store the metric tensor field and exploiting its dedicated hardware to interpolate metric tensor values offered a speedup of 2.5 times over the simple CUDA code.

In order to carry out this research, we built an extensible mesh adaptation framework, which could be the base for future development projects. Using the same framework, it was estimated that the algorithmic complexity of the anisotropic mesh adaptation problem is  $\Theta(n^2)$ , *n* being the number of mesh vertices. Finally, the experience gained throughout this project led to some interesting conclusions on the ease of programming and expected performance from nVIDIA's CUDA as it is compared to IBM's Cell Broadband Engine, based on the author's former experience with the latter platform [RPK<sup>+</sup>10].

#### **1.5** Statement of Originality

This report represents my own work and to the best of my knowledge it contains no materials previously published or written by another person for the award of any degree or diploma at any educational institution, except where due acknowledgement is made in the report. Any contribution made to this research by others is explicitly acknowledged in the report. I also declare that the intellectual content of this report is the product of my own work, except to the extent that assistance from others in the project's design and conception or in style, presentation and linguistic expression is acknowledged.

### **1.6 Report Outline**

The rest of the report is organised as follows: Chapter 2 gives a comprehensive description of the main principles and algorithms that govern the topic of Anisotropic Mesh Adaptivity. More precisely, Section 2.1 contains a description of the concepts behind anisotropic problems and mesh adaptivity, along with optimisation-based algorithms, and Section 2.2 describes the framework upon which these algorithms can be executed in a parallel architecture. Chapter 3 is an introduction to the basics of the CUDA architecture, presenting CUDA's basic architectural points and outlining some key points and strategies used to achieve high performance on this platform. In Chapter 4 we describe the design choices and the actual implementation of the target application, the classes which encapsulate the entities of the adaptivity problem, the data structures used, various code optimisations that have been investigated while trying to improve execution performance and, finally, a list of difficulties we encountered during the development phase of this application. Chapter 5 presents performance diagrams for CUDAMesh64 running in single-threaded mode, OpenMP-mode and CUDA-mode. Based on output meshes, we also try to estimate the algorithmic complexity of the anisotropic mesh adaptivity problem. Finally, Chapter 6 summarises the main concepts, the important papers, the experience gained throughout this project and lists the topics that remain open for further study and future work.

## Chapter 2

# **Background Theory**

This chapter describes the necessary background knowledge the reader should be familiar with before proceeding to the rest of the report. The research is based on two major subjects, the numerical analysis topic of Anisotropic Mesh Adaptivity and the general-purpose computing architecture of nVIDIA's CUDA, which is described in Chapter 3. Both of them need to be briefly introduced along with references to a collection of documents and publications, which provide more in-depth details on these topics.

## 2.1 Anisotropic Mesh Adaptivity

#### 2.1.1 Partial Differential Equations and Meshes

Fluid Dynamics is the science that studies problems related to the motion of fluids. As in all other physics problems, a fluid dynamics problem is modelled using mathematical formulations such as differential and integral equations. In particular, we study such problems using a set of PDEs known as *Navier-Stokes Equations*. In most cases, these equations cannot be solved in an analytical way, so we turn to numerical methods. On common approach is known as *Finite Element Method* (FEM), in which the problem space of the equation under consideration is discretised into smaller sub-regions, usually of triangular (in two dimensions) or tetrahedral (in three dimensions) shape. These sub-regions, referred to as *elements* or *facets* form what is called a *mesh*. The equation is then discretised and solved on this mesh, inside each sub-region.

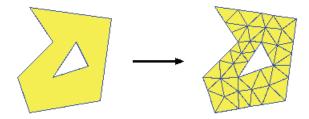

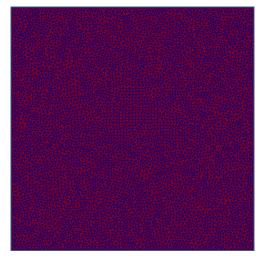

If there is no regular pattern in the topology of elements in a mesh, the mesh is said to be *unstructured*. Unstructured meshes offer greater flexibility in the Finite Element Method, but their representation is more complex and models based on unstructured meshes exhibit higher computational cost compared to structured mesh models. [PFW<sup>+</sup>09]. An example of space discretisation which results in an unstructured mesh is shown in Figure 2.1 [cL99].

The numerical solution process can be seriously affected by the quality of space discretisation. Common discretisation techniques often provide us with poor quality meshes and this has the side effect of both slowing down convergence speed and degrading solution accuracy [FJP95]. This is the point where mesh improving techniques, which reside in the wider context of *adaptive algorithms*, come to the foreground. After solving the PDE on the initial mesh and making a posteriori estimations about solution errors we can spot problematic areas and perform these optimisation techniques, which decide on the quality of a mesh element using some kind of local quality metric (for example, minimum

Figure 2.1: Example of space discretisation, resulting in an unstructured mesh. (Figure from [cL99])

element angle) and try to improve element size, angles and ratio; in other words, they try to "adapt" the mesh towards the correct solution.

This process is summarised in Algorithm 1. The first step consists of solving the equation on the initial mesh and spotting the areas where the solution error is greater than a pre-defined tolerance. Then the adaptive algorithm tries to improve mesh quality and, therefore, solution accuracy. This loop is repeated until solution error reaches an acceptable level.

```

Algorithm 1 General algorithm for the adaptive solution of a PDE.

```

```

Mesh mesh = new Mesh(PDE);

mesh.adapt();

PDE.solveOn(mesh);

while(PDE.getSolutionErrorEstimation() > USER_DEFINED_THRESHOLD)

{

Set S = {elements of low quality};

mesh.adapt();

PDE.solveOn(mesh);

}

```

#### 2.1.2 Objective Functionals: Element Size and Shape

The quality and, therefore, the suitability of a mesh element is determined by some criterion. Common quality criteria include the size of element angles, the aspect ratio between element edges, element size and element shape. Mathematically, these criteria are expressed in the form of an objective functional, i.e. a functional the value of which corresponds to the "height" of quality.

Vasilevskii & Lipnikov proposed a functional [VL99] which takes both element size and shape into account. The functional is defined as:

$$Q_M(\Delta) = \underbrace{12\sqrt{3} \frac{|\Delta|_M}{|\partial\Delta|_M^2}}_{I = \frac{1}{2}} \underbrace{F\left(\frac{|\partial\Delta|_M}{3}\right)}_{I = \frac{1}{2}} \underbrace{F\left(\frac{|\partial\Delta|_M}{3}\right)}_{I = \frac{1}{2}}$$

In the functional above,  $|\Delta|$  denotes the element area of an element  $\Delta$  and  $|\partial\Delta|$  denotes its perimeter. F(x) is a smooth function defined as

$$F(x) = \left[\min\left(x, \frac{1}{x}\right)\left(2 - \min\left(x, \frac{1}{x}\right)\right)\right]^{3}$$

which has a single global maximum of 1 in x = 1 and decreases as we move towards 0 or  $\infty$ , with  $F(0) = F(\infty) = 0$ . The first factor expresses the element quality based on its shape, whereas the

second factor controls the size of element edges. For an equilateral triangle with edges of length l, the first factor evaluates to 1. For any other triangle, this factor evaluates to < 1. Additionally, the second factor evaluates to 1 for a triangle with edges the sum of which is equal to 3, e.g. an equilateral triangle with edges of unit length, otherwise it evaluates to < 1. Taking these two factor together, the objective functional reaches its maximum for an equilateral triangle with sides of unit length; in any other case, the objective functional evaluates to < 1.

Usually, and in the scope of this project, we consider the value of the objective functional for the entire mesh or a mesh cavity to be equal to the value of the element with the lowest quality in the mesh or cavity, respectively.

#### 2.1.3 Anisotropic PDEs

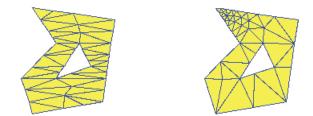

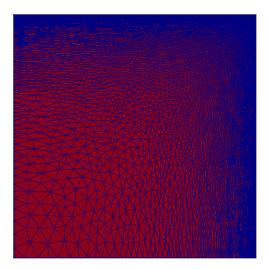

A problem is characterised as "anisotropic" if its solution exhibits directional dependencies. In other words, an anisotropic mesh contains elements which have some (suitable) orientation. An example of an anisotropic mesh is shown in Figure 2.2 [cL99]. The process of anisotropic mesh adaptation begins with a (usually automatically) triangulated mesh as input and results in a new mesh, the elements of which have been adapted according to some error estimation. This estimation is given in the form of a *Metric Tensor*. In the scope of this project, we assume that the error estimation in given to us and we do not examine how it can be calculated. An example of gradually adapting a mesh to the requirements of an anisotropic problem is shown in Figure 2.3 [AMC06].

Figure 2.2: Example of an anisotropic mesh. Mesh elements have different shape and size in different locations on the mesh. (figure from [cL99])

The error estimation gives information about how big or small a mesh element should be. In 1-D, the solution error inside an element e (i.e. a line segment) is defined as

$$\varepsilon = h_e^2 \mid \frac{\partial^2 \psi}{\partial x^2} \mid$$

where  $h_e$  is the length of element e and  $\psi$  is the solution variable. In multi-dimensional problems, the error is defined as

$$\varepsilon = u^T \mid H \mid u$$

where H is the Hessian of the solution equation and u is a vector which shows the ideal length and orientation of element e. In simpler words, the higher the error inside an element e the smaller this element has to become [PUdOG01].

#### 2.1.4 Metric Tensors

In the last equation, the vector u is constructed according to a metric tensor M, i.e. a tensor which, for each point in the 2-D (or 3-D) space, represents the desired length and orientation of an edge

Figure 2.3: Example of anisotropic mesh adaptation. On the left, the process begins with an automatically triangulated mesh, which was not created with with the error estimation in mind. This fact has an impact on the solution error, which is depicted in the bottom left figure. After one refinement iteration (middle figures) the mesh is better adapted to PDE's anisotropy and the solution error is greatly reduced. After two iterations (right figure) the results are even better. (figure from [AMC06])

containing this point. As was the case with the PDE itself, the metric tensor is also discretised; more precisely, it is discretised node-wise. The value of the error between mesh nodes (points) can be taken by interpolating the error from nearby nodes.

The objective functional introduced earlier involved the area and the perimeter of an element E. These quantities are defined with respect to a metric M. If we are in the standard Eucleidian space, the functional reaches its maximum when we have a mesh consisting of uniformly sized, equilateral triangles. In an anisotropic problem we can use the quantities of area and perimeter if we express them with respect to a non-Eucleidian metric  $M(\mathbf{x})$ . For an element E with area  $|\Delta|_E$  and edges of length  $\mathbf{e}_i$  in the standard Eucleidian space, its area with respect to the metric  $M(\mathbf{x})$  can be calculated as

$$|\Delta|_{M} = \sqrt{\det(M)} |\Delta|_{E}$$

and it perimeter as

$$|\partial \Delta|_{M} = \sum_{i=1}^{3} \|\partial \mathbf{e}_{i}\|_{M} = \sum_{i=1}^{3} \sqrt{\mathbf{e}_{i}^{T} M \mathbf{e}_{i}}$$

where we consider that M is constant over the element E, both for simplicity and numerical implementation.

Adapting a mesh so that it distributes the error uniformly over the whole mesh is, in essence, equivalent

to constructing a uniform mesh consisting of equilateral triangles with respect to the metric M. This concept can be more easily seized if we give an analogous example with a distorted space like a piece of rubber that has been stretched (see Figure 2.4). In this example, our domain is the piece of rubber and we want to solve a PDE in this domain. According to the objective functional by Lipnikov (2.1.2), all triangles in the distorted (stretched) piece of rubber should be equilateral with edges of unit length. When we release the rubber and let it come back to its original shape, the triangles will look compressed and elongated, a picture that resembles Figure 2.3.

Figure 2.4: Example of mapping of triangles between the standard Eucleidian space (left shapes) and metric space (right shapes). In case ( $\alpha$ ), the elements in the physical space are of the desired size and shape, so they appear as equilateral triangles with edges of unit length in the metric space. In case ( $\beta$ ), the triangle does not have the desired geometrical properties, so it does not map to an equilateral triangle in the metric space.(Figure from [PFW<sup>+</sup>09])

The metric is defined in such a way that an edge of an element is of unit length with respect to this metric if it has the desired error  $\epsilon_u$  indicated by this metric, i.e.

$$M = \frac{1}{\epsilon_u \mid \bar{H} \mid}$$

The metric tensor M can be decomposed as

$$M = Q\Lambda Q^T$$

where  $\Lambda$  is the diagonal matrix, the components of which are the eigenvalues of M and Q is an orthonormal matrix consisting of eigenvectors  $Q^i$ . Geometrically, Q represents a rotation of the axis system so that the base vectors show the direction to which the element has to be stretched and  $\Lambda$  represents the amount of distortion (stretching). Each eigenvalue  $\lambda^i$  represents the ideal length of an edge in the direction  $Q^i$ . If we denote the diagonal values of the Hessian of the solution as  $h^i$ , then each eigenvalue  $\lambda^i$  is defined as

$$h^i = \frac{1}{\sqrt{\lambda^i}}$$

so that stretching or compressing an element will be done in an inverse square fashion with respect to the error metric  $[PFW^+09]$ .

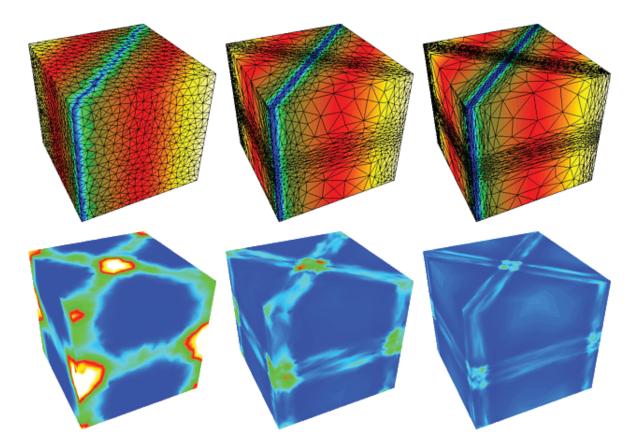

#### 2.1.5 Vertex Smoothing

Vertex smoothing is an adaptive algorithm which tries to improve mesh quality by relocating existing mesh vertices. Contrary to other techniques, vertex smoothing has the advantage of leaving the mesh topology intact. All elements affected by this relocation form an area on the mesh called *cavity*. Essentially, a cavity is defined by its central, free vertex and all incident vertices. A vertex smoothing algorithm tries to improve the quality of cavities containing bad elements. Optimisation takes into account only elements belonging to the cavity, which means that only one vertex is considered for relocation at a time. In other words, the scope of optimisation is the cavity, therefore vertex smoothing

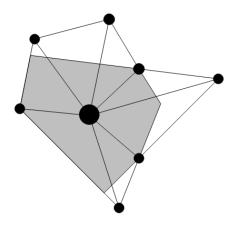

is said to be a *local* optimisation technique. The algorithm moves towards the global optimum through a series of local optimisations. An example of optimising a cavity is shown in Figure 2.5 [Rok10].

Figure 2.5: Vertex smoothing example. The vertex under consideration is the one marked with a big black circle. The local problem area is the light-orange one. All neighbouring vertices are denoted with small black circles. Left figure shows the local problem cavity before smoothing. Right figure shows the result of local smoothing. [Rok10]

The local nature of vertex smoothing leads to the need for optimising a cavity over and over again. After having smoothed a vertex, smoothing an incident vertex in the scope of its cavity may change the quality of the first cavity. Because of this property, the algorithm has to be applied a number of times in order to bring things to an equilibrium. The need for multiple iterations dictates that the local optimisation kernel should be computationally inexpensive. The process is summarised in Algorithm 2. Although the number of iterations to reach an equilibrium is given as a user-defined constant, it is not known a priori how many iterations will be needed and, in fact, it is not even guaranteed that the global optimum can be reached [FJP98]. Convergence criteria could also be used to terminate the algorithm, e.g. if the number of vertices smoothed during the last iteration is zero, then the loop terminates. Following subsections describe the algorithms used in this research to solve the local optimisation problem.

```

Algorithm 2 The vertex smoothing algorithm running MAX_ITER times.

```

```

Set S = {vertices that should be relocated};

int iteration = 0;

while(iteration < MAX_ITER)

{

for(Vertex v : S)

v.relocate();

iteration++;

}

```

### 2.1.6 Laplacian Smoothing

Laplacian Smoothing is one of the most common smoothing algorithms, which just places the vertex to the geometric centre of all vertices surrounding the cavity. Denoting a vertex's coordinates as  $(x_i, y_i)$ ,

the new position for a central vertex in a cavity, defined by N surrounding vertices, is the arithmetic mean of all surrounding vertices:

$$\begin{aligned} x_{central} &= \frac{1}{N} \sum x_i, \forall (surrounding \; vertex)_i \\ y_{central} &= \frac{1}{N} \sum y_i, \forall (surrounding \; vertex)_i \end{aligned}$$

Although computationally cheap, this method does not yield optimal results (it can actually worsen mesh quality) and, what is worse, can even end up returning an invalid cavity, in which some elements have been inverted and have negative area [Fre97]. Invalidation comes as a result of violating the *Interior Convex Hull* restriction. This convex hull of a cavity is an area within which relocation has to be restricted. An example of a cavity and its convex hull is depicted in Figure 2.6.

Figure 2.6: Example of an cavity and its interior convex hull. If the vertex under consideration is relocated outside the grey zone, some elements will have negative area and the mesh will be invalid.

The problems of Laplacian Smoothing can be avoided using *Optimisation-based smoothing*, a family of algorithms which try to optimise an objective functional, retaining validity of meshes and guaranteeing that the resulting cavities will be at least of the same quality as the initial ones. All this comes at the cost of heavier computational load, which is not necessarily a bad thing, as long as we are considering parallel implementations where, as it is known, heavy kernels favour scalability (of course, this does not mean that they also favour performance!). Therefore, optimisation-based smoothing is a perfect candidate for floating-point capable and massively parallel architectures like CUDA. The optimisation-based algorithms used in this research are described in the following sub-sections.

#### 2.1.7 Algorithm by Freitag et al.

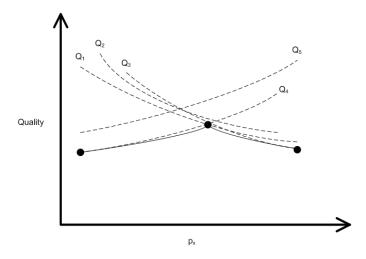

Vertex smoothing is a process which aims at maximising the quality of the worst element in a cavity. Recall that the quality of an element is measured using some objective functional, like the one proposed by Vasilevskii and Lipnikov [VL99]. The implied functional for the whole cavity can be defined as the even infinity norm of all quality functionals associated with the elements of this cavity. This description defines an optimisation problem for each individual cavity in the mesh. The following is a description of the optimisation problem and the solution proposed by [FJP95], as it is described in our previous work [Rok10].

"If we symbolise the cavity as  $C_i$ , its interior convex hull as  $H_i$  and the set of all elements inside  $C_i$

as  $A_i$  then the function we want to maximise is:

$$\phi\left(\mathbf{p}\right) = min\left(Q_{M_{\left(\Delta\right)}}(\mathbf{p})\right), \forall \Delta \in A_{i}$$

A projection on the x-field of an example  $\phi(\mathbf{p})$  is shown in Figure 2.7. As can be seen in that figure, each  $Q_{M_{(\Delta)}}(\mathbf{p})$  is a smooth and differentiable function. Moving along a line of  $Q_{M_{(\Delta)}}(\mathbf{p})$ , there are more than one elements  $\Delta$  that tend to obtain the minimum value. We say that these elements form the *active set* A. The active set, however, changes at the points denoted by black circles in the figure and at these points  $Q_{M_{(\Delta)}}(\mathbf{p})$  is non-differentiable. In order to find the position  $\mathbf{p}$  of the central vertex for which the worst element quality is maximised, we have to solve the non-smooth optimisation problem

$$max(\phi(\mathbf{p})), \mathbf{p} \in H_i$$

This problem has a solution at some point  $\mathbf{p}_s$  if all directional derivatives of  $\phi(\mathbf{p})$  at  $\mathbf{p}_s$  are nonnegative. This solution is unique because all functions  $Q_{M_{(\Delta)}}(\mathbf{p})$  are monotonic while we move towards a fixed search direction. The non-smooth problem can be solved using a technique similar to the *Gradient Descent* method. This method, also called *Steepest Descent*, is used when we deal with twice-differentiable functions. The modified algorithm for non-smooth functions is the one described in Algorithm 3.

Figure 2.7: Projection of an example  $\phi(\mathbf{p})$  on the x-field.

Let the original position of the central vertex be  $\mathbf{p_{init}}$ . At first, the algorithm calculates the interior convex hull of the cavity under consideration and chooses a starting point  $\mathbf{p_0}$ . If  $\mathbf{p_{init}}$  does not coincide with  $\mathbf{p_s}$ , in which case we already have the optimal location for the central vertex and the algorithm exits, then a first guess for  $\mathbf{p_0}$  is the geometric centre  $\mathbf{p_c}$  of this hull. If this guess coincides with  $\mathbf{p_s}$ then the algorithm stops. Recall that the criterion to determine whether  $\mathbf{p_s}$  has been found is that all directional derivatives of  $\phi(\mathbf{p})$  at this guess-point are non-negative. If  $\mathbf{p_c}$  does not coincide with  $\mathbf{p_s}$  then the algorithm decides which point ( $\mathbf{p_{init}}, \mathbf{p_c}$ ) corresponds to a larger value for  $\phi(\mathbf{p})$  and sets it as the starting point  $\mathbf{p_0}$ .

Having found a starting point, the algorithm iteratively tries to find a solution. At every estimationpoint  $\mathbf{p}_i$  the algorithm calculates all directional gradients. The search direction, i.e. the "overall" steepest direction, is calculated by taking the gradients of all  $Q_{M_{(\Delta)}} \in A_i$  and finding all possible convex linear combinations of them (the latter implies solving a respective quadratic programming problem). After that, the algorithm has to decide how to move along the search direction, i.e. solve the "line search sub-problem". This task is accomplished by predicting the points at which the active set  $A_i$  will change. This prediction can be made by taking the first-order Taylor series approximation of  $Q_{M_{(\Delta)}}(\mathbf{p}), \forall Q_{M_{(\Delta)}} \in A_i$  and calculating the intersection of each such approximation with the projection of  $\phi(\mathbf{p})$  in the search direction. The distance between  $\mathbf{p_i}$  and the intersection point closest to it is the initial step length. If moving  $\mathbf{p_i}$  along the search direction by this length improves  $\phi(\mathbf{p})$  by {the estimated improvement  $\pm$  some percentage} ([FJP95] propose  $\pm 10\%$ ) then this length is accepted and  $\{\mathbf{p_i} + step\_length \times search\_direction\}$  becomes the new estimation-point  $\mathbf{p_i}$ . Otherwise, the step length is halved again and again until either a suitable length is found or the step length becomes smaller than a user-defined threshold. Additionally, a step is accepted on the condition that the next step improves  $\phi(\mathbf{p})$  by a smaller amount.

The process described in the paragraph above is repeated until one of the following conditions are met:

- 1.  $\mathbf{p_i}$  coincides with  $\mathbf{p_s}$

- 2. the step length becomes smaller than the user-defined threshold

- 3. the improvement of  $\phi(\mathbf{p})$  between two successive steps falls below a user-defined threshold

- 4. the number of iterations exceeds a pre-defined value"

#### 2.1.8 Algorithm by Pain et al.

When solving the optimisation problem, we can also use non-differential methods, like the one described by [PUdOG01]. Recall that the optimal cavity is the one in which all triangles are equilateral with edges of unit length with respect to some error metric. In essence, the algorithm described here is *Laplacian Smoothing* in metric space.

Given a cavity  $C_i$ , it consists of a central vertex  $V_i$  and all its adjacent vertices  $V_j$ . Let  $L_i$  be the set of all edges the one end of which is the central vertex and the other end is one of the adjacent vertices. The aim is to equate the lengths of all edges  $\in L_i$ . The length of an edge l in metric space is defined as  $r_l = (u_l^T M_l u_l)$ . In order to have (as much as possible) equilateral triangles, we want to minimise the following functional:

$$E_i = \frac{1}{2} \sum_{l \in L_i} r_l^2 = \frac{1}{2} \sum u_l^T M_l u_l$$

If this functional is differentiated with respect to the position  $p^i$  of the central vertex and expressing the edge length in the standard Eucleidian space as  $u_l = p^i - y_l^i$ , where  $y_l^i$  is the position of an adjacent vertex  $V_j$ , then

$$\frac{\partial E_i}{\partial p^i} = \sum_{l \in L_i} M_l u_l$$

At the minimum of the above functional:

$$\sum_{l \in L_i} M_l p^i = \sum_{l \in L_i} M_l y_l^i - q^i = 0$$

where  $q^i = \sum_{l \in L_i} M_l y_l^i$ . If we define  $A^i = \sum_{l \in L_i} M_l$ , then we can calculate the position  $p^i$  using the equation  $A^i p^i = q^i$ . In order to ensure diagonal dominance and insensitivity to round-off error, a new diagonal matrix  $D^i$  is introduced so that the last equation can be written as

$$(D^{i} + A^{i})(p^{i} - \hat{p}^{i}) = q^{i} - A^{i}\hat{p}^{i}$$

```

Algorithm 3 The optimisation-based smoothing algorithm by Freitag et al. [FJP95].

Cavity c = {cavity under consideration};

Function phi = {function phi(p)};

Point pInit = c.getCentralPoint();

Function gradPhi = phi.getGradientFunction();

if(gradPhi.isNonNegativeInAllDirectionsAt(pInit))

return;

Point p = c.getConvexHull().getGeometricalCentre();

if(gradPhi.isNonNegativeInAllDirectionsAt(p))

{

c.setCentralPoint(p);

return;

}

if(c.testMinimumAngleWithCentre(p) <</pre>

c.testMinimumAngleWithCentre(pInit))

p = pInit;

int iteration = 0;

double step = INF;

while(!gradPhi.isNonNegativeInAllDirectionsAt(p) &&

iteration < MAX_ITERATIONS && step > MIN_STEP_LENGTH &&

c.getLastImprovement() > MIN_IMPROVEMENT)

{

Direction searchDirection = c.findSteepestDirectionAt(p);

step = p - c.getClosestIntrPointInDirection(searchDirection);

while((c.testMinAngleImprAt(step, searchDirection) <</pre>

0.9 * c.getEstimatedImpr() ||

c.testMinAngleImprAt(step, searchDirection) <</pre>

c.testMinAngleImprAt(step / 2, searchDirection))

&& step > MIN_STEP_LENGTH)

{

step /= 2;

}

if(step > MIN_STEP_LENGTH)

p += step * searchDirection;

iteration++;

}

c.setCentralPoint(p);

```

where  $\hat{p}^i$  is the initial position of the central vertex and the diagonal matrix is defined as

$$D_{jk}^{i} = \begin{cases} \max A_{jj}^{i}, (1+\sigma) \sum_{m=1, m \neq j} |A_{jm}^{i}|, & \text{if } j = k \\ 0, & \text{if } j \neq k \end{cases}$$

The value of  $\sigma$  is taken to be  $\sigma = 0.01$  in this project. Finally, it is important to use relaxation of  $p^i$  for consistency reasons, using  $x^i = wp^i + (1 - w)p^i$ ,  $w \in (0, 1]$ . In this project, w = 0.5 and the new position of the central vertex can be found by solving the the equation

$$(D^{i} + A^{i})(x^{i} - \hat{p}^{i}) = w(q^{i} - A^{i}\hat{p}^{i})$$

In the case of boundary vertices, i.e. vertices which are allowed to move only along a line (the mesh boundary), a modification of the above algorithm has to be used. The restriction that the vertex can only move along a line means that the new position  $x^i$  can be calculated using the equation

$$x^i = a^i_C u^i_l + \hat{p}^i,$$

where  $u_l^i$  is the unit vector tangent to the boundary line and  $a_C^i$  is the displacement along this line measured from the initial position  $\hat{p}^i$  of the vertex.  $a_c^i$  can be calculated from the equation

$$(D^i + \hat{M}^i)a_c^i = wg^i,$$

where

$$\hat{M}^i = u_l^{i^T} \sum_{l \in L_i} M_l u_l^i$$

and

$$g^i = \sum_{l \in L_i} u_l^{iT} M_l(x^i - \hat{p}^i).$$

#### 2.1.9 Rescaling the metric tensor

The main characteristic of vertex smoothing is that it does not change mesh topology, i.e. the number of mesh elements remains constant and the mesh is not coarsened or refined. In this case, because we cannot refine or coarsen the mesh, it is important to rescale the metric tensor field so that the expected number of elements, as defined by the metric tensor, is equal to the current number of elements. The expected number of elements can be defined as:

$$E_{new} = \frac{\sum_{e=1}^{E_{old}} A_e^{\Omega}}{\theta}$$

where  $E_{old}$  is the current number of mesh elements,  $A_e^{\Omega} = A_e \sqrt{\det(\mathbf{M}_e)}$  is the area of a triangle in metric space ( $A_e$  is the area of this element in the standard Eucleidian space) and  $\theta = \frac{\sqrt{3}}{4}$  is the area of an ideal element in metric space. If  $E_{new} \neq E_{old}$ , then the metric **M** has to be rescaled, so that we end up with a new metric  $\mathbf{M}_{new} = \beta \mathbf{M}$ .  $\beta$  is a scalar value which must satisfy the following condition:

$$E_{new} = \frac{\sum_{e=1}^{E_{old}} A_e \sqrt{\det(\beta \mathbf{M}_e)}}{\theta},$$

which gives that

$$\beta = \frac{\theta E_{new}}{\sum_{e=1}^{E_{old}} A_e \sqrt{\det(\mathbf{M}_e)}}.$$

## 2.2 Parallel Execution

This section gives a description of how vertex smoothing can be run in a parallel fashion, based upon the parallel framework proposed by [FJP98]. Parallel execution means that data are distributed over participating processing units. It is important to ensure *correct execution*, i.e. retain consistency of distributed data and get the same results out of the parallel algorithm as if we ran a serial one. In order to satisfy this requirement, we use the concepts of *elemental operations* and the *operation task* graph, a graph with respect to which the elemental operations must be synchronised.

Trying to ensure data consistency is one of the main reasons why parallel execution performance can be hindered. Being very strict on this consistence requirement would lead to a degeneration of the parallel algorithm into a sequential one. [FJP98] introduce the concept of *elemental operations* and propose that data consistency is maintained only *between* successive executions of these operations and *not during* their execution. This requirement leads to the formulation of the elemental operation steps:

- (a) parallel execution of a set of some mesh improving techniques in each participating processing unit and

- (b) global reduction between these units to update data modified by a.

Retaining data consistency essentially means three things. First of all, there cannot exist two processing units sharing ownership of the same data. Secondly, every mesh vertex has to know exactly what its neighbouring vertices are, i.e. which these vertices are (e.g. their IDs) and their position on the mesh. Neighbouring relationship has to be reciprocal, i.e. if processor 1 knows that its vertex  $v_1$  has as neighbour processor 2's vertex  $v_2$ , then processor 2 must also know that  $v_2$  has  $v_1$  as neighbour. Finally, every mesh element unit has to know its adjacent elements as well. Once again, this relationship has to be reciprocal. A more formal formulation of these requirements is given in [Rok10] based on the proposal by [FJP98]:

"The type of data structures depends on the problem under investigation, the algorithm used and the specific implementation of this algorithm. The research group that proposed this parallel framework ([FJP98]), however, believe that the following properties must be fulfilled for every type of distributed data structures used:

- Every piece of mesh data (vertices, edges and elements) is owned by a unique processing unit no two processors can share ownership of the same data.

- Vertex data have to retain their consistency. After any elemental operation, every vertex v has to know which its neighbours are, i.e. adj(v). This knowledge has to be consistent, i.e. a vertex u is neighbour of v if and only if  $v \in adj(u)$  in the processing unit owning vertex u. In other words,  $G_V$  has to be consistent across all processors. Knowing a neighbour means knowing which vertex it is (for example its global index number) and its position on the mesh.

- Element neighbour data have to retain their consistency. After any elemental operation, every element t has to know which are its neighbours, i.e. adv(t). In other words,  $G_T$  has to be consistent across all processors. This knowledge can be used to perform some important operations, for example calculating a quality metric of two neighbouring elements in order to decide whether an edge-flip will improve local quality."

## 2.2.1 Operation Task Graph

The operation task graph G is a graph the vertices of which represent the elemental operations that have to be accomplished and the edges represent dependencies between operations. If the input of operation  $op_2$  depends on operation  $op_1$  then vertices  $v_1$  and  $v_2$  are connected by an edge. Edges are undirected, i.e. if  $(v_1, v_2) \in G$ , then also  $(v_2, v_1) \in G$ . The task graph is an essential structure as it allows us to extract *independent sets* of operations that can be executed in parallel. After executing an independent set of operations, we have to update neighbouring data (vertices, edges and elements) of the operations' results. At this point it is guaranteed that the distributed data structure will be consistent, since all operations executed were independent from each other. The general algorithm can be seen in Algorithm 4.

```

Algorithm 4 General parallel algorithm for the mesh refinement process.

TaskGraph G = Problem.createTaskGraph();

Set S = new Set(G.getTasksToBeAccomplished());

while(!S.empty())

{

Set R = new Set();

while(!S.empty())

{

Set I = new Set(S.getIndependentSet());

I.executeElementalOperationsOnAllElements();

I.updateElements(I.getAdjacentElements());

R.add(I.getAdjacentElements().spawnElementalOperations());

}

S.setEqualTo(R);

}

```

This algorithm consists of two loops. The outer loop is call the *propagation* loop, because it spawns new elemental operations to adjacent entities (e.g. cavities, elements etc.). In the case of vertex smoothing, for example, once a cavity C defined by the central vertex  $V_C$  has been optimised, the cavities defined by all vertices adjacent to  $V_C$  have to be re-optimised, since a change in cavity C's geometry may have affected their quality. As for the inner loop, the number of iterations performed depends on the task graph and, more importantly, the way independent sets are extracted from it. The nature of vertex smoothing implies that the elemental operations can run asynchronously and mostly require only one-to-one communication between processing units (for other optimisation algorithms a few global reductions would also be required). This property is very important in the scope of efficiency and scalability of a parallel application.

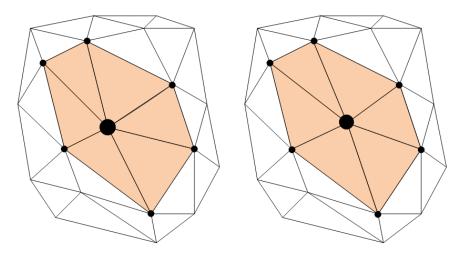

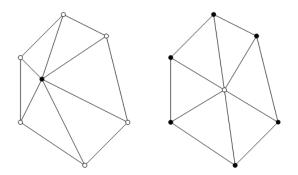

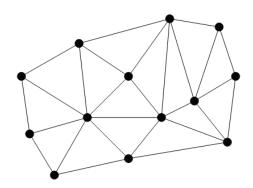

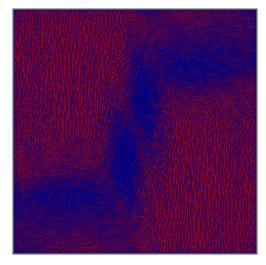

### 2.2.2 Vertex Smoothing Elemental Operation

Executing the algorithm in parallel, we cannot smooth arbitrarily any vertices simultaneously. As can be seen in Figure 2.8, when we smooth a vertex, all adjacent vertices have to remain at their old positions. This means that the independent set of vertices to be smoothed contains vertices that are not adjacent. After smoothing, all neighbouring vertices must have their adjacency lists updated with the new position of the smoothed vertex. Algorithm 5 describes this elemental operation. The task graph is the vertex graph  $G_V$  which is essentially the representation of the mesh itself, as can be seen in Figure 2.9.

Next up, having presented the concept of Anisotropic Mesh Adaptivity, the main algorithms involved in

Figure 2.8: Example of how vertex smoothing should be performed. The left figure shows that in order to smooth the vertex denoted by a black circle we need to know the positions of all adjacent vertices (white circles). In the right, figure we see that all adjacent vertices must be updated with the new position of the smoothed one.

Figure 2.9: Example of a vertex graph  $G_V$ . If we ignore the exact shape of mesh elements, the same drawing could depict the mesh itself.

it and the way it can be run in a parallel fashion, we proceed to present nVIDIA's CUDA architecture, which is the platform of choice for this project, on which (platform) we attempted to implement all the above ideas.

```

Algorithm 5 Algorithm describing vertex smoothing elemental operation.

Vertex v = vertex under consideration;

v.smooth();

if(v.positionChanged())

{

v.getAdjacentVertices().updateWithNewPosition(v.getPosition());

R.add(v.getAdjacentVertices());

}

```

## Chapter 3

# nVIDIA's CUDA Architecture

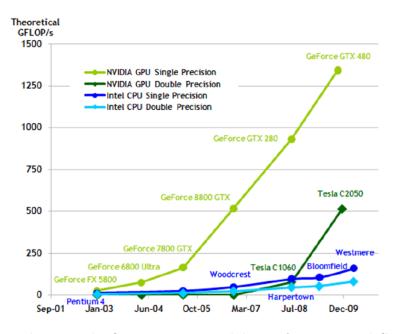

nVIDIA's Compute Unified Device Architecture constitutes one of the most promising trends in modern processor industry. Over the past two decades, the evolution of 3D games pushed semiconductors industry to fabricate more and more powerful graphics processing chips. Gaming requirements have led to the advancement of GPUs to the point where GPU performance in floating–point arithmetic exceeded that of traditional CPUs. Up to recent years, all this tremendous processing power was intended to be used only for graphics and video processing purposes. The concept of General Purpose GPU Computing is a modern trend which aims at unleashing GPU processing capabilities and making them available to a wider range of compute intensive applications. A comparison between CPU and GPU floating-point capabilities over the past decade can be seen in Figure 3.1.

Figure 3.1: Comparison between the floating-point capabilities of conventional CPUs and GPUs over the years. (Figure from [nC10a])

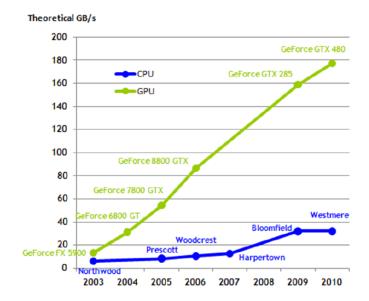

Memory latency and limited bandwidth are generally considered to be two main bottlenecks in highperformance computing. High floating-point capabilities should be accompanied by high memory bandwidths and modern GPUs seem to have address this problem pretty well in comparison to traditional CPUs. Figure 3.2 shows the evolution of memory bandwidth over the past years.

CUDA is nVIDIA's attempt to enter the GPGPU market, which targets not only home and enterprise

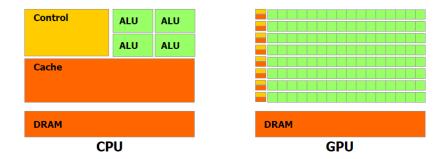

users, but also the supercomputing field. The advantages of CUDA over conventional architectures lie on the way GPUs are designed to manipulate data. Contrary to a general purpose CPU, a graphics processor is designed to "apply the same shading function to many pixels simultaneously" or, in the case of GPGPU computing, "apply the same function to many data simultaneously" [cfd08]. Massive data processing means that GPUs can execute thousands of threads at the same time and are equipped with high bandwidth interconnection between processing cores and memory. This renders them perfect candidates for compute–intensive applications, but not for control–intensive tasks.

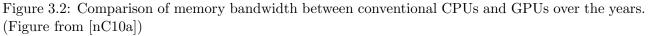

As can be seen in Figure 3.3, the main difference between a GPGPU and a traditional CPU is their floating-point capability. A GPGPU "is specialized for compute-intensive, highly parallel computation exactly what graphics rendering is about and therefore designed such that more transistors are devoted to data processing rather than data caching and flow control" [nC10a].

Figure 3.3: Traditional processing units devote transistors both to execution units and cache memories. CUDA, on the other hand, devotes more area to data processing. (Figure from [nC10a])

## 3.1 Architectural Overview

The philosophy behind CUDA programming is indissolubly bound with its massive data processing capability. The program is written to be executed by one thread and is finally instantiated multiple

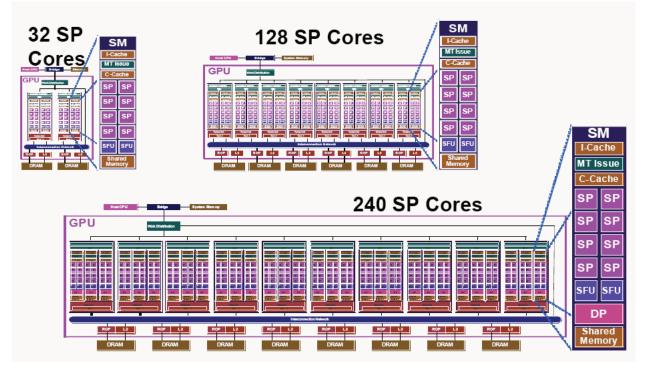

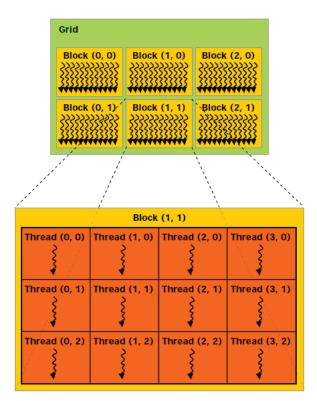

times so that it is executed by many threads running in parallel. This model implies that the program has to be scalable in order to gain the most out of CUDA's hundreds of cores and thousands of threads. Depending on which GPU model is used, the number of available cores, therefore available execution threads, can vary. A general overview of this architecture can be seen in Figure 3.4 [cud08b]. The GPU consists of a number of *multi-processors*, each one containing 8 smaller *stream-processors*. Considering that a typical graphics card can have up to 30 multi-processors and each multi-processor can execute up to some hundreds of threads, a single GPU device can run simultaneously up to some thousands of threads.

Figure 3.4: Overview of CUDA architecture. [cud08b]

### 3.1.1 Memory Model

A CUDA program consists of small pieces of code called *kernels*. Each kernel is executed simultaneously on many cores by multiple threads. All threads run exactly the same code, but may manipulate different data. The GPU communicates with the CPU through the PCI–Express bus. These two processing units have different address spaces, but data can be transferred between them. Explicit data transfer is mandatory and the CUDA API provides all necessary functions. Attempt to dereference a CPU address on the GPU or vice versa will likely result in a crash. Each thread has its own local storage (mainly in form of GPU core registers). Additionally, GPUs are equipped with 16KB per multiprocessor on–chip memory which is two orders of magnitude in terms of latency and one order of magnitude in terms of bandwidth faster than system memory. For devices of *compute capability* over 2.0, like the one used in this project (Fermi architecture), the on–chip memory is 64KB large and can be used both as software-managed shared memory and as a hardware-managed L1 cache. This memory can be shared between all threads of the same block but is inaccessible to any other thread. Figure 3.5 summarises memory hierarchy on a CUDA device and Table 3.1 describes properties of various memory levels [nC10a].

The graphics-processing roots of CUDA have left an important heritage which a GPGPU program can take advantage of: *Texture Memory*. Texture memory is writeable only from the host-side, whereas

| Туре      | Location | Access | Scope             |

|-----------|----------|--------|-------------------|

| Registers | On-chip  | R/W    | Thread            |

| Local     | Off-chip | R/W    | Thread            |

| Shared    | On-chip  | R/W    | Thread–Block      |

| Global    | Off-chip | R/W    | Device & Host CPU |

| Texture   | Off-chip | R      | Device & Host CPU |

| Constant  | Off-chip | R      | Device & Host CPU |

Table 3.1: Memory hierarchy on a CUDA device

Figure 3.5: Memory hierarchy in a CUDA device. (figure from [nC10a])

a CUDA kernel can use in read-inly mode. Reading data from texture memory can have a lot of performance benefits, compared to global memory accesses. Texture memory is cached in texture cache, therefore reading texture data will involve a memory access only on a cache miss. Due to the nature of textures, the texture cache is optimised for 2D spatial locality. The main advantages of texture memory can be summarised in the following points:

- If memory accesses do not follow the patterns required to get good performance (as is the case with global memory), higher bandwidth can be achieved provided there is some locality on texture fetches.

- Addressing calculations are executed automatically by dedicated hardware outside processing elements, so that CUDA cores are not occupied by this task and the programmer does not have to care about addressing.

- Packed data can be broadcast to separate variables in a single operation.

- Integer data (8-bit or 16-bit) can be automatically converted to floating-point values in the range of [0.0, 1.0] or [-1.0, 1.0] [nC10a].

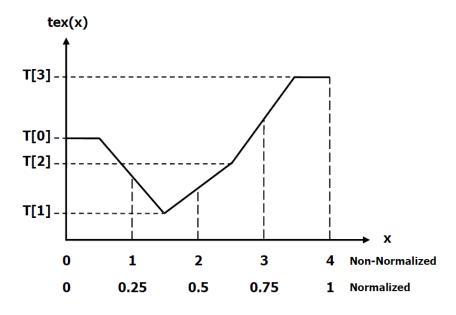

Textures are discretised data from a (theoretically) continuous domain. In graphics processing, there may be needed a texture value from a coordinate which falls between discretisation points. In this case, there has to be performed some kind of texture data *filtering*. The nature of graphics textures resembles the metric tensor field used in anisotropic mesh adaptivity problems. As was described earlier, the metric tensor is discretised vertex-wise. However, when moving vertices during the optimisation process, the new vertex location will most possibly not coincide with a discretisation point. If this is the case, the value of the metric tensor field can be found by interpolating the values from the four nearest discretisation points. This is completely analogous to the most common type of texture filtering, *Linear Filtering*. An example of linear filtering is shown in Figure 3.6.

Figure 3.6: Example of 1D linear texture filtering. (figure from [nC10a])

In two dimensions, the result tex(x, y) of linear filtering is

$$tex(x,y) = (1-\alpha)(1-\beta)T[i,j] + \alpha(1-\beta)T[i+1,j] + (1-\alpha)\beta T[i,j+1] + \alpha\beta T[i+1,j+1]$$

where  $\alpha$  is the horizontal distance of point (x, y) from the nearest texture sample (discretisation point) T[i, j] and  $\beta$  is the vertical distance. The key point is that, when using texture memory, this calculation is automatically performed by dedicated texture hardware outside multiprocessors. When using a conventional CPU or a GPU reading texture from global memory, the above calculation has to be performed by CPU / CUDA cores as part of the execution flow, which has to be programmed manually and occupies execution resources.

From the analysis above, we reach the conclusion that there are two issues of benefit when we make use of texture memory for the metric tensor field. Performance can benefit from texture caching as well as hardware implementation of interpolation. In the scope of this project, we did not evaluate the individual contribution of these two issues. This evaluation would be very interesting, especially when 3D adaptivity problems are considered, and is left as future work. In a 3D problem we have to interpolate the values of the 8 nearest neighbours:

$$tex(x, y, z) = (1 - \alpha)(1 - \beta)(1 - \gamma)T[i, j, k] + \alpha(1 - \beta)(1 - \gamma)T[i + 1, j, k] + + (1 - \alpha)\beta(1 - \gamma)T[i, j + 1, k] + \alpha\beta(1 - \gamma)T[i + 1, j + 1, k] + + (1 - \alpha)(1 - \beta)\gamma T[i, j, k + 1] + \alpha(1 - \beta)\gamma T[i + 1, j, k + 1] + + (1 - \alpha)\beta\gamma T[i, j + 1, k + 1] + \alpha\beta\gamma T[i + 1, j + 1, k + 1]$$

(3.1)

and doing so would require (compared to 2D problems) double the data volume to be fetched from global memory and more than double the floating-point operations if we do not use hardware implementation of interpolation.

#### 3.1.2 Programming Model

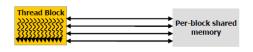

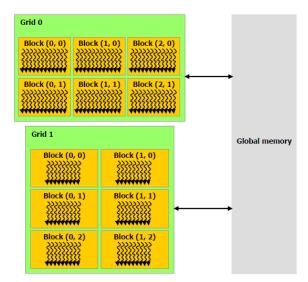

A great advantage of programming on CUDA is that it is very similar to conventional C/C++ programming and it is fairly easy to port existing codebase onto the new platform. Even if writing entirely from the beginning, parallel programming on CUDA is much more effortless than on other platforms, e.g. developing applications for the Cell Broadband Engine require writing code specifically for Cell's execution cores. A CUDA kernel is executed by many threads. These threads are grouped into so called *thread blocks* and each thread within a block is identified by thread and block ID variables (akin to processor rank number in MPI). Using these identifiers it is possible to specialise the execution path of each thread. Blocks are executed one per multi-processor. The special thing about a block is that all threads within it can communicate via shared memory and synchronise with each other. All blocks form what is called a *grid*. Grids are executed one per GPU device. This description is illustrated in Figure 3.7 [nC10a]. IDs of blocks are 2-coordinate ones and each block's ID is unique within a grid. Following the same convention, IDs of threads are 3-coordinate ones and each thread's ID is unique within a block. Grid dimensions are instantiated during application launch [cud08a].

Figure 3.7: Threads and blocks in a CUDA device. [nC10a]

Specialising the execution path of threads, however, can degrade performance. If two threads within the same *warp* (a warp is a group of 32 threads that are created/managed/scheduled/executed in parallel) need to diverge their execution paths, then these executions will be serialised, i.e. the first path will be executed while the thread following the second path is stalled and after that the thread following the first path will be stalled while the second threads is executed.

An important principle in CUDA programming is that blocks must be independent from each other.

They can be executed in any order, in series or in parallel, and coordinate their execution. However, having shared locks between blocks to achieve coordination can not only lead to deadlocks but also degrade application scalability, the latter being destructive considering the philosophy behind CUDA. Synchronisation between CPU and GPU can be implemented using the CUDA API. When CPU code calls a kernel to be executed on a GPU, control returns to CPU immediately and the kernel is executed asynchronously. On the other hand, data transfer calls are blocking ones. There are non-blocking versions of these calls and this allows us to overlap computation and communication, therefore increasing performance and favouring scalability.

Additionally, there are calls which synchronise all threads within a block, i.e. they put a barrier at that particular point in execution which must be reached by all threads in the block before execution can continue [cud08a]. Unfortunately, blocks cannot synchronise with each other. The only way to synchronise two or more blocks is to wait for the kernel to finish execution and then re-launch it. This action definitely involves some overhead which can degrade performance. However, the cost is not detrimental, because CUDA threads are lightweight an invoking a kernel is much cheaper than creating, for example, an OS thread.

#### 3.1.3 Execution Model

As was mentioned earlier, a CUDA program consists of small pieces of code called kernels. Kernels are instantiated many times and each instance is executed by a dedicated thread. Many threads form a thread–block which is executed on a multi–processor. One multi–processor may have many concurrent thread–blocks, the number of which depends on the available hardware resources, i.e. on–clip shared memory and register file. A thread–block is organised in *warps*, each one consisting of 32 threads and being executed in a SIMD fashion. Many thread–blocks form a grid, which is executed on a CUDA device. This device is dedicated to its grid, i.e. there cannot be two or more grids under execution on a device at the same time [cud08c].

## **3.2** Code Optimisations

In this subsection we will try to describe some general guidelines that maximise execution performance on a CUDA device. These ideas are basically what was proposed at [cud08c], which in turn is a comprehensive summary of nVIDIA's guidelines.

#### 3.2.1 Memory Optimisations

A CUDA device is equipped with a memory system similar to other high-performance platforms, like the Cell Broadband Engine. General rules for these platforms also apply here. Bandwidth is much higher for inter-device communication than between host CPU and device GPU. Therefore, the latter communication should be minimised. Additionally, every data transfer has a certain amount of overhead, independently of transfer size, so one large transfer is preferable to many small ones. Communication between host and device can be enhanced by taking advantage of CUDA's ability to allocate *page-locked* system memory. This technique maximises bandwidth for memory copy operations. Moreover, the application should be written in such a way so that computation and communication are overlapped. This is possible on CUDA thanks to its asynchronous memory copy operations. Hiding communication latency behind computation not only favours performance but also application scalability to more cores and devices.

Data alignment in memory is also an important factor in achieving good bandwidth utilisation and high performance. Depending on the device's *compute capability*, an access to global (device) memory can be serviced by as few as 1 or 2 transfers. Accessing misaligned data, however, is followed by many more memory transactions and performance can be seriously degraded. A way to address this problem is utilisation of fast, on-chip shared memory, which can be used as a data re-alignment buffer for data to be stored back to global memory (apart from its obvious uses as a means of thread synchronisation within a block and global memory caching).

Shared memory accesses, however, have their own rules. This memory is divided into banks. Successive 32-bit words are allocated to successive banks. Each bank can be accessed by one thread at a time. If two or more threads try to access the same bank simultaneously, requests will be serialised. If there are no bank conflicts, shared memory can service simultaneously as many requests as the number of its banks. Access speed is the same as for the register file. As is the case with shared memory, global memory is also divided into *partitions*. Successive 256-byte sets of data are assigned to successive partitions. Partition access should follow a pattern similar to that of shared memory. If many threads try to access (either read of write) the same partition performance will be degraded and the phenomenon is called *partition camping*.

#### 3.2.2 Execution Configuration Optimisations

As is the case with every other multi–threaded platform, instructions within a thread are executed sequentially, so if a thread stalls for some reason (data dependencies, data transfers) hardware utilisation is reduced. This problem can be addressed by running many warps on a multi–processor. General guidelines are the following:

- The number of thread–blocks must be larger than the number of multi–processors so that every multi–processor has at least one block to run.

- Even better, the number of thread-blocks should be al least twice the number of available multiprocessors so that even if a thread-block stalls (e.g. waiting on memory), the multi-processor will continue to be busy executing the other block.

- If we want to take into account future GPUs which will incorporate even more multi-processors, the number of thread-blocks should be even larger than the previous case.

Additionally, thread–block size should be multiple of warp size so that there are no under–occupied warps that waste resources.

## 3.3 C++ support

Although nVIDIA provides full support for C code, C++ is only partially supported by the CUDA compiler. C++ features that can be used by devices of compute capability 2.0 (Fermi architecture) are the following:

- Polymorphism

- Default parameters

- Operator overloading

- Namespaces

- Function templates

- Classes

More specifically on class support, any class function can be compiled to CUDA object code as long as this function is not virtual (a restriction that will be removed in future architectures). Moreover, all functions are inlined by the compiler because CUDA hardware is not capable of calling functions. Unfortunately, the linker cannot link two functions that belong to different object files and this is the reason why all classes must reside in the same source file.

Having presented both the topic of Anisotropic Mesh Adaptivity and nVIDIA's CUDA architecture, which comprise the essential background the reader should be familiar with, we go on to the next chapter where we describe the design choices we had to make and the actual implementation of CUDAMesh64.

# Chapter 4

# **Design and Implementation**

This chapter contains a thorough description of the application which was developed as a way for us to evaluate the performance of anisotropic mesh adaptation. There is a description of the object-oriented model the code-base is built upon, the data structures that are used to represent all useful information about the adaptivity problem and the optimisations that were applied in our effort to improve CUDA performance. Design and implementation were guided to a great extent by [nC10a] and [nC10b]. At the end of the chapter, there is a list of problems that were encountered during the development and optimisation phases. Apart from benchmarking purposes, the application described in this chapter is also a stand-alone application, called *CUDAMesh64*, which can be used in the solution of real adaptivity problems.

### 4.1 Design choices

Before proceeding to the description of the actual implementation, it is necessary to list the design choices we had to make at the beginning of this implementation and the reasons why we took these specific decisions.

The first thing we had to specify was the target platform of this application. We chose to work on nVIDIA's *Fermi* architecture, i.e. devices with compute capability 2.0. Apart from being the stateof-the-art among CUDA architectures, *Fermi* offers better C++ support than previous generations, which is an important feature when it comes to code development and testing compared to pure C. Another advantage, and maybe the reason that renders *Fermi* mandatory choice, is its capabilities in double-precision floating-point arithmetic. Contrary to older compute capabilities, where double-precision data had to be broken down into pairs of single-precision values, *Fermi* overcomes this limitation and manipulates double-precision data just like it does with single-precision ones.

Double-precision arithmetic was chosen over single-precision because it is the standard choice in the world of scientific applications. The choice of higher precision is indicated by the need to make the application more robust to the order in which arithmetic operations take place (a quite common problem in numerical analysis) and reduce round-off errors. In addition, structuring our application on double-precision data gives us the chance to assess Fermi's double-precision capabilities and make more meaningful comparisons between CPU and GPU, since in today's CPUs even single-precision variables are represented internally as double-precision ones.

Mesh adaptivity can be carried out using different families of algorithms. The most common families are h-adaptivity and r-adaptivity. The first one includes algorithms which change mesh topology by adding vertices and edges, creating new elements by bisection or adaptive refinement, flipping

edges etc. [Rok10]. The family of *r-adaptivity* algorithms, on the other hand, includes techniques that leave mesh topology intact. *Vertex Smoothing* is an *r-adaptivity* algorithm. Not modifying mesh connectivity makes implementation much easier. Both the number of mesh vertices and their connectivity remain constant and so does the operation task graph, i.e. there is no need to re-colour the graph after every iteration over the mesh when running in parallel. Moreover, vertex smoothing is a computationally demanding technique and this property helps in showing off CUDA's capabilities in floating-point arithmetic and exhibiting large speedups over conventional platforms.

As was mentioned in the introductory chapter, there is a related project called *Fluidity*. We decided to build *CUDAMesh64* independently of *Fluidity*'s data structures, using our own ones. *CUDAMesh64* is not part of *Fluidity* but rather an independent component for a mesh bases simulator which can be coupled with any simulator. Having data structures customised for the specific problem of vertex smoothing would allow us to optimise the application in a better way and achieve higher performance.

As far as graph colouring is concerned, we chose to implement a single-threaded and greedy colouring algorithm, called *First Fit Colouring* [AOS06]. Although being a greedy algorithm, *First Fit* runs adequately fast and still colours the mesh with satisfactorily few colours. These properties, along with the simplicity of implementation, indicated that *First Fit* is just fine for the purpose of this project, so parallel algorithms or more sophisticated colouring techniques were not deemed necessary.

As will be described in later sections, one of the optimisations we can enable in our code is having dedicated texture hardware interpolate metric tensor values. This interpolation can be done using either *nearest-point sampling* or *linear filtering*. We chose to use the latter method, because nearest-point sampling can be very unsuitable, especially when the metric tensor field has a lot of discontinuities.

The whole application and all auxiliary frameworks used throughout this project are compiled and used in 64-bit mode, hence the name *CUDAMesh64* of the target application. The reason behind our choice of this mode is not that it is really needed at this time but because this framework was built with extensibility and scalability in mind. Problems become more complex and so do the data representing them. It is a matter of just a couple of years until hardware requirements of an adaptivity problem exceed the order of magnitude in which we worked in this project. There is already the *Tesla C2070* card which is based on *Fermi* architecture and hosts 6GB of device memory. Future architectures are expected to host amounts of memory well above the 32-bit limit of 4GB.

# 4.2 Meshes and the VTK framework