# Remote-Scope Promotion: Clarified, Rectified, and Verified

John Wickerson

Imperial College London, UK j.wickerson@imperial.ac.uk

Bradford M. Beckmann

Advanced Micro Devices, Inc., USA brad.beckmann@amd.com

Mark Batty

University of Kent, UK

m.j.batty@kent.ac.uk

# Alastair F. Donaldson

Imperial College London, UK alastair.donaldson@imperial.ac.uk

#### **Abstract**

Modern accelerator programming frameworks, such as OpenCL<sup>TM</sup>, organise threads into work-groups. *Remotescope promotion* (RSP) is a language extension recently proposed by AMD researchers that is designed to enable applications, for the first time, both to optimise for the common case of intra-work-group communication (using *memory scopes* to provide consistency only within a work-group) and to allow occasional inter-work-group communication (as required, for instance, to support the popular load-balancing idiom of *work stealing*).

We present the first formal, axiomatic memory model of OpenCL extended with RSP. We have extended the HERD memory model simulator with support for OpenCL kernels that exploit RSP, and used it to discover bugs in several litmus tests and a work-stealing queue, that have been used previously in the study of RSP. We have also formalised the proposed GPU implementation of RSP. The formalisation process allowed us to identify bugs in the description of RSP that could result in well-synchronised programs experiencing memory inconsistencies. We present and prove sound a new implementation of RSP that incorporates bug fixes and requires less non-standard hardware than the original implementation.

This work, a collaboration between academia and industry, clearly demonstrates how, when designing hardware support for a new concurrent language feature, the early application

of formal tools and techniques can help to prevent errors, such as those we have found, from making it into silicon.

Categories and Subject Descriptors C.1.4 [Processor Architectures]: Parallel Architectures; D.3.1 [Programming Languages]: Formal Definitions and Theory

*Keywords* Formal methods, graphics processing unit (GPU), Isabelle, OpenCL, programming language implementation, weak memory models, work stealing

# 1. Introduction

Remote-scope promotion (RSP) is a new accelerator programming feature that was recently proposed by a team of AMD researchers [19]. In a nutshell, RSP allows two popular accelerator programming paradigms – memory scopes and work stealing – to be unified for the first time. Simulation of a prototype GPU implementation has demonstrated that applications using RSP perform on average 17% faster than those using only memory scopes, and 6% faster than those that use only work stealing. This encouraging result indicates that the feature has the potential to be included in future GPUs.

In this work we scrutinise the complex and subtle design of RSP and reason rigorously about its correctness using formal techniques. We report on our findings, presenting the technical details of our RSP formalisation, and highlighting the role our formal approach played in identifying bugs in the original design.

This work stems from a collaboration between AMD researchers and an academic team of formal semanticists. Our collaboration was made possible by AMD's decision to publish details of new processor features very early in their design cycle, a departure from the more closed approach typical among processor vendors. We report on bugs that we found in the RSP design, demonstrating the value of applying formal techniques from the academic research community and collaborating *early* during the design of hardware support for a new concurrent programming language construct.

This is the author's version of the work. It is posted here for your personal use. Not for redistribution. The definitive version was published in the following publication:

OOPSLA'15, October 25–30, 2015, Pittsburgh, PA, USA © 2015 ACM. 978-1-4503-3689-5/15/10... http://dx.doi.org/10.1145/2814270.2814283

Using a combination of a proof assistant (Isabelle [18]),<sup>1</sup> a cutting-edge memory modelling tool (HERD [3]), and recent advances in modelling the behaviour of heterogeneous programming languages (e.g., [24]), we have translated the original proposal for RSP, which encompasses both high-level programming language extensions and low-level architectural extensions, into rigorous mathematics. We have discovered and identified fixes for several bugs with the previously-described design, improved its clarity both for users and implementers, proposed several modifications that simplify the design and may improve its performance, and proved the soundness of the implementation (after applying our fixes and improvements).

Our work is distinguished from other efforts to formalise the semantics of complex processor architectures [1, 3, 16, 22, 23], by its focus on a *prototype* architecture that is several years away from fabrication. We therefore deliberately focus on an idealised model. This enables rapid development, and leads to what we regard as the key value of our work: identifying fixes and improvements to the RSP design to be made *at very little cost*. In contrast, errors and bugs discovered late in the design cycle or errors that make it into silicon can be extremely expensive to fix or work around.

We report the following research contributions:

- 1. Formalising the OpenCL+RSP language (§3) We describe precisely how the OpenCL<sup>TM</sup> framework for heterogeneous parallel programming can be extended to capture RSP; we call the extension OpenCL+RSP.

- 2. Testing OpenCL+RSP programs (§4) We have extended the HERD litmus test simulator [3] to enable enumeration of the allowable outcomes of small OpenCL+RSP programs. This allows developers to understand how key concurrency idioms at the heart of their algorithms might behave on any (current or future) correct implementation of OpenCL+RSP. We applied HERD to a set of 12 AMD OpenCL+RSP litmus tests and an AMD work-stealing queue implementation, revealing issues in four of the litmus tests and a data race in the work-stealing queue implementation. These issues have been confirmed and fixed.

- 3. Formalising the implementation of OpenCL+RSP (§5) Informed by the published design [19] and collaboration between the authors and other AMD designers, we present a formalisation of the original implementation of OpenCL+RSP. This comprises a mathematical model of a simple GPU device, semantics for a minimal assembly language for this device, and a scheme for compiling OpenCL+RSP to this assembly language.

The formalisation process led to the discovery of two bugs in the initially proposed design of RSP, one that violates the atomicity of atomic read-modify-write (RMW) operations, and one that renders the *message-passing* idiom unusable.

This idiom is central in lock-free concurrency and used at the heart of work stealing, the key motivator for OpenCL+RSP. We confirmed the message-passing bug to occur twice in the prototype implementation. A third potential instance of this bug was actually avoided in the prototype implementation by the inclusion of cacheline stalls, which prevent certain problematic interactions; but these stalls were not mentioned in the description of the implementation. These two scenarios respectively illuminate how formalisation can help designers not only to make correct designs, but to understand which details make their designs correct.

- 4. Improving the implementation (§5.4, §5.5) Our formalisation also identified several significant simplifications that can safely be made to the OpenCL+RSP implementation: by reordering certain low-level instructions, the bugs we found can be fixed without the need for expensive cacheline stalls. Importantly, this avoids the need for non-standard hardware to support cacheline stalling, a prerequisite of the original implementation proposal. Additionally, the avoidance of stalling may improve the efficiency of the implementation.

- 5. A proof of soundness (§6) Finally, we prove that our improved implementation is sound, in that it does provide the required high-level semantics. More precisely: we show that every low-level execution of a compiled OpenCL+RSP program is contained in the set of executions that are allowed for the program with respect to the high-level semantics. Our soundness result provides a firm basis for designers looking to support RSP in their next-generation GPU architectures.

**Online companion material** We provide Isabelle scripts containing type-checked definitions for our formalisation of RSP, and an extended write-up of our (non-mechanised) soundness proof, at the following webpage:

http://multicore.doc.ic.ac.uk/RSP/

# 2. Background: Remote-Scope Promotion

# 2.1 Heterogeneous Programming with OpenCL

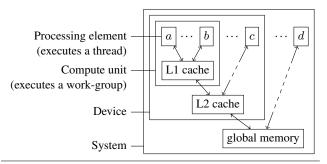

The OpenCL programming framework [17] provides a *hierarchical execution model*, geared towards heterogeneous systems made up of CPUs, GPUs, and other accelerators. Each thread<sup>2</sup> is identified according to the *work-group* to which it belongs, and the device on which that work-group is executing. A thread executes on a *processing element* and a work-group on a *compute unit*. A similarly-structured *memory hierarchy* comprises a private memory region per thread, a region shared among threads in a work-group (e.g., an L1 cache), a region shared among work-groups on a device (e.g. an L2 cache), and a global region available to the whole system. High performance can be achieved by restricting data sharing to lower levels of the memory hierarchy where possible, minimising memory latency. Figure 1 illustrates the execution and memory hierarchies.

<sup>&</sup>lt;sup>1</sup> As discussed further in §5, we have used Isabelle to formalise and type-check our definitions and theorem statements; we have *not* mechanically proved the theorems.

<sup>&</sup>lt;sup>2</sup> Threads in OpenCL are also called *work-items*.

Figure 1. Illustration of the OpenCL execution hierarchy

Atomic operations OpenCL 2.0 provides atomic operations, which enable fine-grained lock-free synchronisation both within and between work-groups and devices. The operations provide a range of memory-consistency guarantees according to semantics defined by a detailed C11-based memory model [17: §3.3]. Operations with weaker guarantees may offer superior performance, but have more subtle semantics.

**Memory scopes** Where the OpenCL memory model departs significantly from C11 is in its introduction of *memory scope* constants. The three constants are:

```

s ::= WG current work-group

| DV current device

| ALL all devices

```

and, when attached to an atomic operation, govern how far through the execution hierarchy the memory consistency guarantees must be enforced. For instance, if a global memory location  $\mathbf x$  is currently being accessed only by threads in the same work-group, such as a and b in Fig. 1, the accesses can be scoped at WG so that they need travel no further than the L1 cache that a and b share.

Both participants in a synchronisation operation are required to use a memory scope that is wide enough to encompass the other. This rule would be violated if, for instance, thread a in Fig. 1 writes x at WG scope, thread c (in a different work-group) reads x, and there is no synchronisation in between. As we shall explain further in §2.2, such a situation is deemed by OpenCL to be a race: a programmer fault that renders the whole program undefined.

Work stealing is a technique for achieving dynamic load balancing in high-performance computing. In an OpenCL context, work stealing involves each work-group owning a task queue, and idle threads popping tasks from another work-group's queue should their own queue become empty. The ability to steal work is valuable when it is impractical to distribute tasks evenly among work-groups at compile-time – either because of a non-uniform computational cost per task that depends on input data, or because new tasks can be created dynamically at run-time [8].

To scope or to steal? The current design of OpenCL allows programmers to exploit work stealing, or to exploit the

scoping mechanism, but not both. To see this, consider an application that exploits scopes by having threads use workgroup scope when pushing to or popping from their local task queue. This makes stealing impossible, regardless of the stealer's scope, because synchronisation fails unless *both* of the operations that are synchronising use wide-enough scopes. To make stealing possible, we could arrange that every queue operation uses a wider scope, but then we lose the benefit of using scopes: the common case (accessing one's own queue) would take a performance hit to allow the uncommon case (stealing from another's queue).

A solution: remote scope promotion Previous work proposed an extension to OpenCL's scoping mechanism [19], remote-scope promotion (RSP), that is compatible with work stealing. It was shown that on a range of benchmarks from the Pannotia suite [9] (including Google's PageRank), RSP combined with stealing leads to an average speedup of 17% over scopes alone, and 6% over stealing alone.

In OpenCL extended with RSP (OpenCL+RSP), each atomic operation has an extra Boolean flag, indicating whether the operation is *remote*. In ordinary scoped synchronisation, both of the synchronising operations must use a wide-enough scope. The essence of RSP is to add another sufficient condition for synchronisation; namely, that just one of the participants has a wide-enough scope and is flagged as remote. In this case, the scope of the other participant is irrelevant; it is silently promoted to match the first participant's scope.

A mapping from OpenCL+RSP to hardware primitives was described previously. Remote operations are compiled to special instructions for flushing or invalidating caches that belong to other work-groups or other devices. It was informally argued that the implementation is correct. The implementation has been realised in a simulator and has been tested using a number of examples.

The need for formality Like all new concurrency-related language constructs, RSP has a subtle semantics that may be hard to implement correctly, and is hard to reason about. (For instance, from the prose description above: what should happen when both participants in a pair of synchronising operations are flagged as remote?) Due to the inconclusive nature of testing, and the fundamental problems associated with testing concurrent systems, we turn to formal methods for a rigorous treatment of RSP.

# 2.2 The OpenCL Memory Model

The OpenCL 2.0 memory model, which builds on the C11 memory model, is the part of the OpenCL language specification that covers reading and writing shared memory locations. It defines which values are allowed to be read at a given program point, and whether two memory accesses have a data race. It is principally concerned with the collection of atomic functions, which can expose to programmers the various weak memory behaviours of the underlying hardware.

The C11 memory model was first formalised by Batty et al. [6]; this formalisation was then extended to the OpenCL case by Wickerson et al. [24]. In §3, we extend the memory model further to formalise OpenCL+RSP.

**Axiomatic memory models** All of these memory models are defined axiomatically. To define the set of a program's allowed executions in this style, one first generates a superset thereof, called the set of pre-executions, which comprises those executions that could be obtained with the use of a completely non-deterministic memory that returns an arbitrary value for each load. An 'execution', in this context, comprises a set of run-time memory events (such as  $R_{DV}(x, 42)$ , which indicates the value 42 being read from x using device scope), and several relations between them (such as the program order of the corresponding instructions). One then whittles this down, using a set of axioms, to the set of consistent executions. A pre-execution is consistent if it can be extended to a candidate execution that satisfies all of the axioms of the memory model. A candidate execution additionally contains a reads from relation (representing data flow from write events to read events) and a modification order among the writes to each location. These two relations together constitute the execution witness. If any of a program's candidate executions is deemed to have a data race, the behaviour of the program is undefined, which means that it may behave arbitrarily (and the behaviours of candidate executions that do not have data races become irrelevant).

Syntax of OpenCL programs We restrict our attention to a small OpenCL-like language that includes non-atomic loads and stores (load<sub>na</sub> and store<sub>na</sub>), scoped atomic acquire-loads and release-stores (load<sub>s</sub> and store<sub>s</sub>), and a scoped 'atomic increment' operation (fetch\_inc<sub>s</sub>) that demonstrates an acquire+release RMW. Full OpenCL includes other varieties of atomic memory access, such as relaxed and sequentially-consistent.

In real OpenCL, all threads execute the same kernel program, but can obtain differing control or data flows by querying their own thread identifiers. In our simplified setting, we suppose that each thread is programmed independently. Reflecting the execution hierarchy in OpenCL, we formalise an OpenCL program P as a list of lists of sequential programs:

$$\begin{array}{cccc} P & ::= & P_{\rm dv} \parallel \parallel \ldots \parallel \parallel P_{\rm dv} \\ P_{\rm dv} & ::= & P_{\rm wg} \parallel \ldots \parallel P_{\rm wg} \\ P_{\rm wg} & ::= & p \parallel \ldots \parallel p \end{array}$$

where p is a piece of sequential code,  $\|\|$  separates code executed by different devices,  $\|\|$  separates code executed by different work-groups in the same device, and  $\|$  separates code executed by different threads in the same work-group.

**Example 1.** The following program comprises two threads in two different work-groups on the same device.

$$fetch_{inc_{DV}}(x) \parallel store_{DV}(x, 2)$$

One thread increments x and the other sets x to 2. The use of DV-scope for both operations ensures that these conflicting accesses do not race.

# 2.3 Details of the Memory Model

The details of the OpenCL memory model are summarised in Fig. 2. We give the language from which event labels are drawn – this ranges over read (R), write (W), and read-modify-write (RMW) events (which represent, for instance, an atomic increment or a successful compare-and-swap). We provide identifiers for particular subsets of events in any given candidate execution, and list the basic and derived relations between events. We finally give the axioms of the memory model, following the .cat format of Alglave et al. [3]. Five axioms (the consistency axioms) characterise consistent executions, and one further axiom (the non-faultiness axiom) characterises the absence of data races. We shall explain these axioms further, after introducing the following notational conventions.

**Notation.** We write  $r^+$  for the transitive closure of a relation  $r, r^{-1}$  for its inverse, and we abbreviate  $r \cup id$  as  $r^?$ , where id is the identity relation. We write  $\neg$  for complement,  $\backslash$  for set difference, unv for the universal relation, and [s] to abbreviate  $\{(x,x) \mid x \in s\}$ . We define relational composition (;) such that  $(x,z) \in r_1$ ;  $r_2$  if  $(x,y) \in r_1$  and  $(y,z) \in r_2$  for some y. (This notation is convenient for describing shapes in execution graphs; for instance, the relation  $[s_1]; r_1; [s_2]; r_2; [s_3]$  relates events in  $s_1$  to those in  $s_2$  and then taking an  $r_2$ -edge.)  $\square$

The rs' and rs relations define the *release sequence*, which is inherited without modification from C11 and can be safely ignored by the unfamiliar reader. The incl1 relation connects event  $e_1$  to event  $e_2$  whenever  $e_1$ 's scope is no narrower than the distance between the events in the execution hierarchy at run-time. When this relation also holds in the opposite direction  $(incl^{-1})$ , then the events are deemed to have inclusive scopes, as captured by the incl relation. Interthread synchronisation (sw, 'synchronises-with') relates an atomic write to an atomic read in another thread that reads from it, providing the two events have inclusive scopes. Happens-before (hb) edges are induced both by the program order and by synchronisation. They must not form cycles (Hb); that is, the shape  $\triangle hb$  is forbidden.

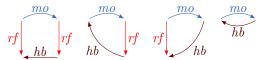

The principle of *coherence* (Coh) governs the relationship between hb and mo: if the write  $w_1$  is mo-before the write  $w_2$ , then  $w_2$  (and any events that read from  $w_2$ ) must not happen before  $w_1$  (nor before any events that read from  $e_1$ ). Coherence forbids the following shapes.

The reads-from axiom (Rf) forbids reads to observe writes that happened after them (hb) The non-atomic reads-

**Location types:** Each location is atomic or non-atomic

**Event labels:** For locations x, scopes s, and values v:

- $W_{na}(x,v)/R_{na}(x,v)$ : non-atomic write/read

- $W_s(x,v)/R_s(x,v)$ : atomic write/read

- RMW<sub>s</sub>(x, v, v'): atomic read-modify-write

# **Predefined subsets of events:**

- R: the set of read and RMW events

- W: the set of write and RMW events

- 1: the set of initialisation events (each a non-atomic write of 0, one per location)

- nal: events that access a non-atomic location

- na: non-atomic events

- WG/DV/ALL: the set of events that are parameterised by the respective memory scope

# **Primitive relations:**

- thd/wg/dv: an equivalence relation over all (noninitialisation) events, relating events from the same thread/work-group/device

- loc: an equivalence relation over all events, relating events that access the same location

- sb (sequenced before): a strict partial order specifying the order of each thread's instructions, and also linking initialisation events to non-initialisation events

- rf (reads from): contained in  $W \times R$ , relating writes to reads when the locations and values match, each read reads from exactly one write

- mo (modification order): a strict partial order that relates all and only writes to the same atomic location

# **Derived relations:**

- $rs' \stackrel{\text{def}}{=} thd \cup (unv; [R \cap W])$

- $rs \stackrel{\text{def}}{=} mo \cap rs' \setminus ((mo \setminus rs'); mo)$

- $\begin{array}{l} \bullet \ rs \stackrel{\text{def}}{=} \ mo \cap rs' \setminus ((mo \setminus rs') \ ; \ mo) \\ \bullet \ incl1 \stackrel{\text{def}}{=} \ ([\texttt{WG}] \ ; \ wg) \cup ([\texttt{DV}] \ ; \ dv) \cup ([\texttt{ALL}] \ ; \ unv) \\ \bullet \ incl \stackrel{\text{def}}{=} \ incl1 \cap incl1^{-1} \\ \bullet \ sw \stackrel{\text{def}}{=} \ ([W \setminus \texttt{na}] \ ; \ rs^? \ ; \ rf \ ; [R \setminus \texttt{na}]) \cap incl \setminus thd \\ \end{array}$

- $hb \stackrel{\text{def}}{=} (sb \cup sw)^+$

- $hbl \stackrel{\text{def}}{=} hb \cap loc$   $vis \stackrel{\text{def}}{=} hb \setminus (hb; [W]; hbl)$   $conflict \stackrel{\text{def}}{=} ((W \times W) \cup (W \times R) \cup (R \times W)) \cap loc$

- $dr \stackrel{\text{def}}{=} conflict \setminus hb \setminus hb^{-1} \setminus incl$

#### **Consistency axioms:**

#### Non-faultiness axiom:

$$\mathbf{empty}(dr) \tag{Dr}$$

**Figure 2.** The OpenCL memory model (simplified)

from axiom (Narf) requires non-atomic reads to observe an immediate predecessor in hb, called a visible write: i.e. we must have  $hb \downarrow rf$  but no hb-intervening write to the same

$$\operatorname{location} \begin{pmatrix} hb \checkmark \\ W \\ hbl \checkmark \\ rf \end{pmatrix}.$$

The principle of RMW atomicity (Rmw) dictates that each RMW event must observe the mo-latest write to that location; that is, it must not observe itself ( rf ), it must not observe a write that is too late  $(mo\sqrt{rf})$ , and it must not observe a

write that is too early

$$\binom{mol}{mol} rf$$

.

Finally, an execution has a data race (dr) if two conflicting events are unrelated by happens-before and do not have inclusive scopes. The non-faultiness axiom (Dr) detects data races.

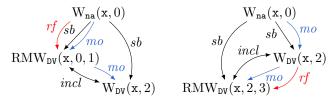

**Example 2.** Here are two executions of the program in Example 1, both of which satisfy all of the consistency axioms and the non-faultiness axiom. The initial event is drawn above the events of the two parallel threads. Reflexive and transitive edges are elided. The left-hand execution gives rise to the final state x = 2, while the right-hand one finishes with x = 3.

Other final values for x are not allowed. For instance, the following execution, which would result in x = 1, falls foul of the Rmw axiom: it constitutes a violation of RMW atomicity.

**Example 3.** If the program in Example 1 were changed so that the increment had work-group scope:

$$fetch_{inc_{WG}}(x) ||| store_{DV}(x, 2)$$

then the scope-inclusion (incl) edges seen in Example 2 would all be replaced with data race (dr) edges.

Simplifications and other discrepancies with the standard We do not consider the distinction between global memory (shared among all threads) and local memory (shared among threads in a work-group), and instead treat all memory as global; local memory is not interesting in the context of memory scopes, since the only allowable scope with which local memory can be accessed atomically is WG. Fences, barriers, relaxed atomics, and sequentially-consistent atomics

were not discussed in previous work on RSP [19] and are largely orthogonal.

OpenCL employs a stricter form of scope inclusion, in which both events must additionally use the *same* memory scope. The version we use here follows a proposal called HRF-relaxed [10], and is a necessary prerequisite for RSP.

# 3. Formalising OpenCL+RSP

We now describe our first research contribution: how to extend the OpenCL memory model with RSP. The purpose of this extension is: (a) to enable programs that exploit RSP to be analysed (§4), and (b) to enable a proof that the implementation of the language features is correct (§5). Note that (b) is an important enabler for (a), because the program analysis would be meaningless were the OpenCL+RSP memory model impossible to implement.

Adding RSP to OpenCL first involves extending the syntax of the language, and to this end, we propose simply to add an additional parameter to each existing atomic function, which accepts either N (for non-remote) or R (for remote) – see Example 4 below. Second, we must extend the semantics of the language (i.e., the memory model). This requires changing just one definition, the *incl* relation in Fig. 2, as follows:

$$incl \stackrel{\text{def}}{=} incl1 \cap incl1^{-1}$$

$\bigcup ([rem]; incl1) \cup (incl1^{-1}; [rem])$

where rem identifies the set of events representing a remote operation. In the original definition, both events must have wide enough scopes; in the new version, the events (say  $e_1$  and  $e_2$ ) may also synchronise if  $e_1$ 's scope is wide enough to reach  $e_2$  and  $e_1$  is remote, or if  $e_2$ 's scope is wide enough to reach  $e_1$  and  $e_2$  is remote.<sup>3</sup>

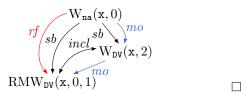

**Example 4.** If the program in Example 3 were changed so that the store became *remote*:

$$fetch_{inc_{WG,N}}(x) \parallel store_{DV,R}(x,2)$$

then the scope-inclusion (incl) edges seen in the executions in Example 2 would be restored.

The simple manner in which we can adapt the memory model for RSP illustrates the elegance of an axiomatic memory model. Our extension is conservative in the sense that it does not affect the semantics of OpenCL programs that do not exploit RSP. It is significantly simpler than a previous outline formalisation [19], and is further distinguished by being founded on an existing, comprehensive formalisation of OpenCL [24]. Although the details of implementing RSP are rather involved (as we discuss in detail in §5), the

effect of RSP on the memory model is minimal. The minor modification to the *incl* relation is all that is required to enable simulation of litmus tests that exploit RSP, which we discuss next.

# 4. Testing OpenCL+RSP Programs

We extended the memory model simulator HERD to support the simulation of small OpenCL+RSP programs against the newly-extended memory model (§4.1). We then used HERD to analyse a suite of test programs that we obtained from the broader group of original RSP developers, uncovering several faults in the process (§4.2), and further exercised HERD to debug a larger OpenCL+RSP application: a work-stealing queue (§4.3).

# 4.1 Extending HERD

HERD is a generic memory model simulator [3]. Its basic operation is to generate and iterate through a set of candidate executions of a given litmus test, and assess whether each is consistent and/or faulty according to the axioms of a given memory model, as described using the .cat specification language. Originally designed for CPU assembly programs [3], HERD has recently been extended with the capacity to simulate C11 and OpenCL programs [24]. For the current work, we have extended HERD further, to support OpenCL+RSP. This entailed two sub-tasks: extending the front end of HERD to understand remote versions of atomic operations in litmus tests, and extending the memory model specification language with an additional identifier, *rem*, to stand for the set of remote events in an execution.

#### 4.2 Litmus Testing

The original developers of RSP used a suite of 12 litmus tests to gain confidence in the correctness of their implementation. These tests, which are mostly variants on standard litmus tests, characterise the building blocks of parallel algorithms that use RSP. We obtained the suite from the RSP developers, and used HERD to simulate each test against our formalisation of the OpenCL+RSP memory model.

**Preparation** We encoded each program into the .litmus format that is accepted by HERD. In doing so, we observed that the original litmus tests make several uses of empty loops that spin until a given location holds a specific value, such as 'while (load(x) != 1); C'. Because such programs have arbitrarily-many candidate executions (one for each possible iteration count) we followed standard practice in preparing litmus tests (e.g., Alglave et al. [1]) and replaced the pattern above with 'if  $(load(x) == 1) \{C\}$ ', ignoring those executions where the conditional test failed.

**Results** We performed simulation on a 2.8 GHz MacBook Pro, and observed that each litmus test was fully simulated in less than one second, except for two tests that made use of several compare-exchange instructions; each of these tests was fully simulated in less than three minutes.

$<sup>\</sup>overline{{}^3}$  We initially sought to encode RSP by instead adding an extra disjunct to the incl1 relation:  $incl1 \stackrel{\mathrm{def}}{=} \ldots \cup ([rem]; unv)$ . Although seductively simple, this version does not capture the intended behaviour of RSP in the case where both participants are marked remote; rather, it would erroneously allow two remote WG-scoped operations to synchronise across different devices.

Seven of the 12 litmus tests included postconditions on the final state of memory that we found, through analysis with HERD, to be satisfied by all consistent executions. Another test exhibited a deliberate data race that was confirmed by HERD.

Our analysis exposed bugs in the other four litmus tests. The first test had an unintentional data race, resulting from a discrepancy between the HSA 1.0 memory model [13] and the OpenCL 2.0 memory model. Specifically, OpenCL does not enforce happens-before between two operations that access different regions of memory even if they belong to the same thread, so one cannot assume the HSA behaviour, which does enforce happens-before here. The second test also contained a data race. The third had an incorrect postcondition due to a simple arithmetic error. The fourth had a postcondition that was too strong: it forbade certain executions that were allowed by the axioms of the memory model. As it happens, the proposed implementation does not give rise to the executions that this litmus test forbids; it can therefore be deemed a conservative implementation of the OpenCL specification in this regard.

# 4.3 Case Study: A Work-Stealing Queue

We used HERD to probe the correctness of a more realistic OpenCL+RSP application: a work-stealing queue. This application, is a key motivator for RSP [19: §3.2], and exploits RSP by simultaneously optimising for the common case of accessing the local task queue (by using WG-scoped non-remote operations in push and pop) and enabling the uncommon case of accessing a different work-group's queue (by using DV-scoped remote operations in steal).

Alglave et al. [1] have uncovered two bugs in a similar CUDA implementation [8] that led to tasks occasionally being dropped from queues; both bugs arose from assuming an overly-strong memory model. This was demonstrated by hand-compiling suspect slices of the CUDA code into GPU assembly litmus tests (named *dlb-mp* and *dlb-lb*) and showing experimentally that these tests could produce results that would lead to bugs at the CUDA level.

We have been able to demonstrate the complementary result for the OpenCL+RSP work-stealing queue. We produced OpenCL+RSP litmus tests capturing the same thread interactions that *dlb-mp* and *dlb-lb* captured at the GPU assembly level. Using HERD, we were able to verify the *absence* of the bugs associated with the original CUDA implementation, thanks to sufficient use of store-release and load-acquire functions to ensure necessary synchronisation. Because our result demonstrates correctness at the level of the programming language, it extends to *any* correct implementation of OpenCL+RSP.

We emphasise that we have not verified the entirety of the work-stealing queue implementation; we merely state that it is free from two specific bugs. Indeed, on the contrary, we found, reported, and confirmed a data race that could arise when performing a pop and a steal on the same queue. The

race, which arises because pop can non-atomically write to the queue's tail pointer while the steal atomically reads from it, can be rectified by upgrading the non-atomic write to a relaxed atomic write.

# 5. A Formalised Implementation of OpenCL+RSP

Having studied the programming language semantics of RSP, we now turn our attention to formalising a low-level implementation of RSP, transforming the published description of the implementation of OpenCL+RSP into rigorous mathematics. Our formalisation comprises a mathematical model of a simple GPU device (§5.1), the syntax and semantics of a minimal assembly language for this device (§5.2 and §5.3) and a scheme for compiling OpenCL+RSP to assembly (§5.4 and §5.5).

Our formalisation effort found several opportunities to improve the original compilation scheme, ranging from improving inefficiencies to eliminating errors. Our revised compilation scheme is simpler than the original and addresses all of the errors and inefficiencies we found, hence we present the revised scheme first (§5.4), then explain the original scheme in terms of how it differs from our proposal (§5.5). In §6 we prove that our revised scheme is sound.

Tool support from Isabelle The definitions in this section have been formalised using the Isabelle proof assistant [18], and the scripts are available in our online companion material. We have also formalised the statement of our soundness theorem (Thm. 1, §6), but have not mechanised its proof. We found the type-checking and custom syntax that Isabelle provides to be invaluable while designing our model. We remark that the semantics of assembly instructions (§5.2), each of which updates various components in a deeply-nested structure of records and lists, is naturally expressed in an imperative style; because Isabelle demands a functional style, our formalisation differs in this respect from the current presentation.

#### 5.1 A Model of GPU Hardware

Our model of GPU hardware closely resembles the illustration in Fig. 1, which in turn is based on the model used for the original design of RSP [19: Fig. 4].

Figure 3a defines the set of states (SyState) that the machine can inhabit; this is defined in terms of numerous other sets, and in some cases we provide the name of a variable we shall use to range over the elements of the set. We use d, w and t to range over device, work-group and thread identifiers, all of which are natural numbers. In Fig. 3a we use an identifier followed by colon to name a component of a tuple so that, for instance, we can refer to the third component of a  $CacheEntry\ E$  by writing E.fr.

Complementing the formal definitions, Fig. 3b gives a pictorial representation of the machine state, rendering each

```

Loc

x \in

SyState

Reg

r \in

Val \stackrel{\text{def}}{=} \mathbb{Z}

DvState

v \in

\mathit{FifoEl} \ \stackrel{\mathrm{def}}{=} \ \mathit{Loc} \cup \{ \mathtt{FLUSH}_{d,w,t} \mid d,w,t \in \mathbb{N} \}

WqState

L1: Cache

Fifo \stackrel{\text{def}}{=} FifoEl queue

ThState

Hygiene \stackrel{\text{def}}{=} \{CLEAN, DIRTY\}

Val

Freshness \stackrel{\text{def}}{=} \{VALID, INV'D\}

CacheEntry \stackrel{\text{def}}{=} Val \times (\text{hy: } Hygiene) \times (\text{fr: } Freshness)

C \in Cache \stackrel{\text{def}}{=} (Loc \rightharpoonup CacheEntry) \times (fifo: Fifo)

(\text{rmw}: Lock)

l \in Lock \stackrel{\text{def}}{=} \{ \mathbf{r} \} \cup \{ \mathbf{d}, \mathbf{w}, \mathbf{t} \mid d, w, t \in \mathbb{N} \}

ThState \stackrel{\text{def}}{=} Reg \rightarrow Val

WqState \stackrel{\text{def}}{=} ThState \text{ list} \times (\text{L1: } Cache) \times (\text{rmw: } Lock)

DvState \stackrel{\text{def}}{=} WqState \text{ list} \times (\text{L2: } Cache) \times

Global

(lockfile: Loc \rightarrow Lock)

Loc | Val

Global \stackrel{\text{def}}{=} Loc \rightharpoonup Val

\Sigma \in SyState \stackrel{\text{def}}{=} DvState  list \times (gl: Global)

(a) Formal definitions

```

(b) A machine state  $\Sigma$ , pictorially

Hygiene

$\sqrt{a}l$

fifo: Fifo

L2: Cache

Val

fifo: Fifo

Loc | Lock

lockfile

Freshness

Hygiene

Figure 3. Machine states

component as a rounded rectangle, and using a stacking effect to indicate a multiplicity of similar components.

The state of the system (SyState) comprises the state of each device plus the contents of global memory, which is a partial function from locations (Loc) to values (Val). We assume that all values are mathematical integers, and that global memory contains any location that is requested.

The state of a device (DvState) comprises the state of each of its work-groups, the contents of the L2 cache, and a 'lock file' that records, for each location, whether it is locked in the L2 cache  $(d, \overline{w}, t)$ , where d, w, t identifies the thread holding the lock) or unlocked (**1**). While a location is locked in the L2 cache by one thread, no other thread can read, write, evict, fetch, or flush it.

The state of a work-group (WqState) comprises the state of each of its threads, the contents of the L1 cache, plus an additional lock that stalls the execution of RMW operations (and is taken by threads executing remote RMW and store operations to ensure atomicity). The state of a thread (ThState) comprises its register file, which is a total function from registers to values. We assume an unlimited number of registers.

A cache (Cache) comprises two components: a partial function from locations to cache entries, and a synchronisation fifo. Each entry (CacheEntry) comprises a value, a hygiene bit (CLEAN or DIRTY), and a freshness bit (VALID or INV'D). Note that each location in memory has a separate cache entry (cf. Remark 1). The synchronisation fifo (Fifo) is a hardware component introduced as part of AMD's QuickRelease technology [11]. It is a queue whose elements (FifoEl)

are locations that may need to be flushed to the lower levels of the cache; by inserting flush markers (FLUSH) among the locations, tagged with their own device/work-group/thread identifier, threads can ascertain which locations have been flushed. We assume that the queue datatype supports in-place enqueue() and dequeue() methods, and exposes a tail field.

**Notation.** We write  $\Sigma_d$  for the state of device d,  $\Sigma_{dw}$  for the state of work-group w in that device, and  $\Sigma_{dwt}$  for the state of thread t in that work-group. When we pass an Loc x to a Cache C, writing C(x), we are implicitly looking up x in the first of C's two components.

# 5.2 Assembly Language

We formalise our assembly language so that the behaviour of each thread in each work-group in each device is specified independently. Accordingly, and in keeping with our formalisation of OpenCL (§2.2), an assembly program is a list (devices) of lists (work-groups) of lists (threads) of lists (instructions of a thread) of assembly instructions.

The assembly language instructions are listed in the lefthand column of Table 1. In summary, we have: loading from a location to a register, storing from a register to a location, atomically incrementing a location in the L1/L2 cache (this being the simplest representative of the class of atomic RMW operations), inserting a FLUSH marker into one or more L1 or L2 caches, invalidating all entries in one or more L1 caches, locking/unlocking a location in the L2 cache, and obtaining/releasing all of the RMW locks in the current work-group/device/system. Other standard instructions, and in particular control flow instructions, would be required to

| Instr.                                                                                                                                                  | Effect on state $\Sigma$ when                                                                                                   |  |  |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------|--|--|--|

|                                                                                                                                                         | executed by thread $(d, w, t)$                                                                                                  |  |  |  |

| $\mathtt{LD}rx$                                                                                                                                         | if $\Sigma_{dw}.\text{L1}(x).\text{fr} = \text{VALID}$ then                                                                     |  |  |  |

|                                                                                                                                                         | $\Sigma_{dwt}(r) := \Sigma_{dw}. L1(x)$ else block                                                                              |  |  |  |

| ST r x                                                                                                                                                  | $store(\Sigma_{dw}.\text{L1}, x, \Sigma_{dwt}(r))$                                                                              |  |  |  |

|                                                                                                                                                         | if $\neg ready_{d,w,t}(\Sigma_{dw}.\text{rmw})$ then block                                                                      |  |  |  |

| INOL1 / x                                                                                                                                               | else if $\Sigma_{dw}$ .L1 $(x) = (v, \_, \text{VALID})$ then                                                                    |  |  |  |

|                                                                                                                                                         | $\Sigma_{dwt}(r) := v$                                                                                                          |  |  |  |

|                                                                                                                                                         | $store(\Sigma_{dw}. \text{L1}, x, v + 1)$ else block                                                                            |  |  |  |

| $INC_{12} rx$                                                                                                                                           | if $\neg ready_{d,w,t}(\Sigma_{dw}.rmw)$ then block                                                                             |  |  |  |

| 112                                                                                                                                                     | else if $\Sigma_{dw}$ .L1(x).hy = DIRTY then block                                                                              |  |  |  |

|                                                                                                                                                         | else if $\neg ready_{d,w,t}(\Sigma_d.\text{lockfile}(x))$ then block else if $\Sigma_d.\text{L2}(x) = (v,\_,\text{VALID})$ then |  |  |  |

|                                                                                                                                                         | $invalidate(\Sigma_{dw}.L1,x)$                                                                                                  |  |  |  |

|                                                                                                                                                         | $\forall d'. invalidate(\Sigma_{d'}. L2, x)$                                                                                    |  |  |  |

|                                                                                                                                                         | $\Sigma_{dwt}(r) := v$ $store(\Sigma_d.L2, x, v + 1)$                                                                           |  |  |  |

|                                                                                                                                                         | else block                                                                                                                      |  |  |  |

| ${\tt FLU_{L1}} \; {\tt WG}$                                                                                                                            | $\Sigma_{dw}$ .L1.fifo.enqueue(FLUSH $_{d,w,t}$ )                                                                               |  |  |  |

| ${\tt FLU_{L1}DV}$                                                                                                                                      | $\forall w'. \Sigma_{dw'}. \text{L1.fifo.enqueue}(\text{FLUSH}_{d,w,t})$                                                        |  |  |  |

| $FLU_{L1}$ SY                                                                                                                                           | $\forall d'. \forall w'. \Sigma_{d'w'}. \text{L1.fifo.enqueue}(\text{FLUSH}_{d,w,t})$                                           |  |  |  |

| ${\tt FLU_{L2}DV}$                                                                                                                                      | $\Sigma_d$ .L2.fifo.enqueue(flush $_{d,w,t}$ )                                                                                  |  |  |  |

| $FLU_{L2}$ SY                                                                                                                                           | $\forall d'. \Sigma_{d'}. \text{L2.fifo.enqueue}(\text{FLUSH}_{d,w,t})$                                                         |  |  |  |

| INV <sub>L1</sub> WG                                                                                                                                    | $\forall x. invalidate(\Sigma_{dw}.L1, x)$                                                                                      |  |  |  |

| INV <sub>L1</sub> DV                                                                                                                                    | $\forall w'. \forall x. invalidate(\Sigma_{dw'}.L1, x)$                                                                         |  |  |  |

| INV <sub>L1</sub> SY                                                                                                                                    | $\forall d'. \forall w'. \forall x. invalidate(\Sigma_{d'w'}. L1, x)$                                                           |  |  |  |

| $\mathtt{LK_{L2}}x$                                                                                                                                     | if $\neg ready_{d,w,t}(\Sigma_d.\text{lockfile}(x))$ then block else $\Sigma_d.\text{lockfile}(x) := d, w, t$                   |  |  |  |

| $\mathrm{UL_{L2}}x$                                                                                                                                     | $\Sigma_d.\text{lockfile}(x) := \blacksquare$                                                                                   |  |  |  |

| LK <sub>rmw</sub> DV                                                                                                                                    | if $\exists w'. \neg ready_{d,w,t}(\Sigma_{d w'}.rmw)$ then block else $\forall w'. \Sigma_{d w'}.rmw := d \cdot w \cdot t$     |  |  |  |

| LK <sub>rmw</sub> SY                                                                                                                                    | if $\exists d'. \exists w'. \neg ready_{d,w,t}(\Sigma_{d'w'}. \text{rmw})$ then block                                           |  |  |  |

| LITTING DI                                                                                                                                              | else $\forall d'. \forall w'. \Sigma_{d'w'}. \text{rmw} := \overline{d, w, t}$                                                  |  |  |  |

| UL <sub>rmw</sub> DV                                                                                                                                    | $\forall w'.  \Sigma_{d  w'}. \text{rmw} := \blacksquare $                                                                      |  |  |  |

| $UL_{\mathtt{rmw}}SY\ \ \forall d'. \forall w'. \Sigma_{d'w'}.rmw := \blacksquare \!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!$ |                                                                                                                                 |  |  |  |

| where:                                                                                                                                                  |                                                                                                                                 |  |  |  |

| $store(C, x, v) \stackrel{\text{def}}{=} C(x) := (v, \text{DIRTY}, \text{VALID})$<br>C.fifo.enqueue(x)                                                  |                                                                                                                                 |  |  |  |

| $ready_{d,w,t}(l) \stackrel{\text{def}}{=} (l = \underline{d, w, t}) \lor (l = \underline{\hspace{1cm}} )$                                              |                                                                                                                                 |  |  |  |

| $invalidate(C,x) \stackrel{\text{def}}{=} \mathbf{if}  C(x) \neq \bot  \mathbf{then}  C(x). \text{fr} := \text{INV'D}$                                  |                                                                                                                                 |  |  |  |

**Table 1.** Semantics of assembly instructions

else nop

provide a complete set; we limit the presentation here to those that manipulate the memory system.

Table 1 also defines the effect of each assembly instruction when executed from state  $\Sigma$  by thread t in work-group w in device d. Formally, each instruction is modelled as a non-deterministic state transformer: a function from SyState to  $\mathcal{P}(SyState)$ . A blocked instruction returns the empty set, denoted **block**. For the time being, no instruction produces more than one final state,  $^4$  so we define each instruction using deterministic, imperative pseudocode. We overload the  $\forall$ -operator to provide an imperative **foreach** construct, leaving the bounds implicit.

These pieces of pseudocode leave only one other aspect of the instructions' behaviours implicit: each piece of pseudocode, *action*, should be made conditional as follows:

if  $unflushed_{d,w,t}(\Sigma)$  then block else action

where

$$\begin{array}{c} unflushed_{d,w,t}(\Sigma) \stackrel{\mathrm{def}}{=} \\ (\exists d'. \, \mathtt{FLUSH}_{d,w,t} \in \Sigma_{d'}. L2. \mathrm{fifo}) \vee \\ (\exists d', w'. \, \mathtt{FLUSH}_{d,w,t} \in \Sigma_{d'w'}. L1. \mathrm{fifo}). \end{array}$$

That is, a thread that has placed a FLUSH marker in an L1 or L2 fifo must block until its marker is dequeued.

**Loads and stores** Regarding loads (LD) from location x: if x's L1 cache entry is valid, the cached value is copied into the register file accordingly. Otherwise, the instruction blocks, waiting for the environment to fetch a valid entry from deeper in the cache hierarchy. In practice, the load would initiate this fetch, but since our interest is in checking safety properties, the existence of an environmental transition that will fetch the new entry means that it suffices to suppose that the load simply blocks. We describe environmental transitions in §5.3.

Stores (ST) to location x simply write to x's L1 entry, adding a new entry if none exists, and overwriting any previous entry. The entry is marked dirty and valid (via the store helper function) and the location is enqueued to the cache's synchronisation fifo.

Atomic increments The INC<sub>L1</sub> and INC<sub>L2</sub> instructions are RMW operations, so they block if the rmw lock is held by another thread. INC<sub>L1</sub> increments x in the L1 cache, writing the original value to the given register; it blocks until the L1 cache holds a valid entry for x (as with loads, we rely on environmental transitions to provide this valid entry). If the L1 entry for x is dirty, the instruction blocks until it is flushed; otherwise, the L1 entry, if present, is invalidated. If access to x's L2 entry is forbidden (by another thread holding x's lockfile entry), then the instruction blocks. The instruction also blocks if x's L2 entry is invalid or absent; otherwise it increments x in the L2 cache. When storing to the L2 cache,

While conducting our soundness proof, we make use of an alternative semantics that 'disengages' the memory system, making loads completely non-deterministic.

all of x's entries in other devices' L2 caches are invalidated (via the  $\forall d'$ .  $invalidate(\Sigma_{d'}.L2,x)$  step), to preserve cache coherence.

Flushes and invalidates The  $FLU_{L1}$  instruction enqueues a flush marker, tagged with the current thread's identifier, into the current L1 cache, or all L1 caches in the current device, or all L1 caches in the system, depending on whether the instruction is parameterised by WG, DV, or SY, respectively.  $FLU_{L2}$  enqueues a flush marker into the current L2 cache, or all L2 caches in the system, depending on whether it is parameterised by DV or SY, respectively. The  $INV_{L1}$  {WG, DV, SY} instruction invalidates all entries in all L1 caches in the {workgroup, device, system}.

**Locks**  $LK_{L2} x$  and  $UL_{L2} x$  respectively lock and unlock the location x in the current L2 cache, the former blocking if the lock is currently held by another thread.  $LK_{rmw}$  and  $UL_{rmw}$  respectively obtain and release all the rmw locks in the given scope. While a work-group's rmw lock is held by one thread, no other thread in that work-group can perform an RMW operation.

Reducing non-standard hardware requirements Some of the instructions above require non-standard hardware support: specifically, the ability for a thread to flush/invalidate caches that are not in its direct path to global memory, to lock cachelines, and to lock RMW operations [19: §4.4]. An attractive feature of the revised RSP implementation inspired by our formalisation effort (§5.4) is that it does *not* use cacheline locking, and thus requires less non-standard hardware.

# 5.3 Environmental Transitions

At any time, the 'environment' can transform the system state. Environment transitions do not correspond to program instructions, but each is triggered by a particular thread.

Locks aside, we point out that if an instruction is blocked, there is always an environmental transition, or a series of environmental transitions, that will result in the instruction becoming unblocked. Locks, meanwhile, present the possibility of deadlock if used carelessly.

The available environmental transitions are defined, in Tab. 2, by their effect on the current system state  $\Sigma$ . Each cell in the right-hand column of the table takes the form **if** precondition **then** action, to reflect the fact that the transition can only occur under certain conditions.

The transitions are: evicting a clean cache entry (EVICT $_{L1}$  and EVICT $_{L2}$ ), flushing a dirty cache entry and marking it clean (FLUSH $_{L1}$  and FLUSH $_{L2}$ ), replacing a clean-or-absent cache entry by fetching from the level below (FETCH $_{L1}$  and FETCH $_{L2}$ ), removing a location whose cache entry is clean-or-absent from the tail of a fifo (DEQLOC $_{L1}$  and DEQLOC $_{L2}$ ), and removing a FLUSH marker from the tail of a fifo (DEQMARKER $_{L1}$ ).

Regarding the Fetch<sub>L1</sub> action, notice that the newly-fetched entry is always marked CLEAN, even if the L2 entry

| Name                                            | Effect on state $\Sigma$ when triggered by thread $(d,w,t)$                                                                                                                                                                                                                                                                              |

|-------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| $EVICT_{L1}(x)$                                 | if $\Sigma_{dw}.\mathrm{L1}(x).\mathrm{hy}=$ clean then $\Sigma_{dw}.\mathrm{L1}(x):=\bot$                                                                                                                                                                                                                                               |

| $EVICT_{L2}(x)$                                 | $\begin{aligned} & \text{if } \Sigma_d. \mathrm{L2}(x). \mathrm{hy} = \mathrm{CLEAN} \\ & \text{and } & ready_{d,w,t}(\Sigma_d. \mathrm{lockfile}(x)) \text{ then} \\ & \Sigma_d. \mathrm{L2}(x) := \bot \end{aligned}$                                                                                                                  |

| $FLUSH_{L1}(x,v)$                               | $\begin{split} & \textbf{if } \Sigma_{dw}.\text{L1}(x) = (v, \text{dirty}, \_) \\ & \textbf{and } ready_{d,w,t}(\Sigma_d.\text{lockfile}(x)) \textbf{ then} \\ & \forall d'.\Sigma_{d'}.\text{L2}(x).\text{fr} := \text{INV'D} \\ & store(\Sigma_d.\text{L2}, x, v) \\ & \Sigma_{dw}.\text{L1}(x).\text{hy} := \text{CLEAN} \end{split}$ |

| $FLUSH_{L2}(x,v)$                               | $\begin{split} & \textbf{if } \Sigma_d. \mathrm{L2}(x) = (v, \mathrm{DIRTY}, \_) \\ & \textbf{and } \operatorname{ready}_{d,w,t}(\Sigma_d.\mathrm{lockfile}(x)) \textbf{ then} \\ & \Sigma.\mathrm{gl}(x) := v \\ & \Sigma_d. \mathrm{L2}(x).\mathrm{hy} := \mathrm{CLEAN} \end{split}$                                                  |

| $\operatorname{Fetch}_{\operatorname{L1}}(x,v)$ | $\begin{array}{l} \textbf{if } notDirty(\Sigma_{dw}.\text{L1},x) \\ \textbf{and } \Sigma_{d}.\text{L2}(x) = (v,\_,\text{VALID}) \\ \textbf{and } ready_{d,w,t}(\Sigma_{d}.\text{lockfile}(x)) \textbf{ then} \\ \Sigma_{dw}.\text{L1}(x) := (v,\text{CLEAN},\text{VALID}) \end{array}$                                                   |

| $FETCH_{L2}(x,v)$                               | $\begin{aligned} & \textbf{if} \ notDirty(\Sigma_d.\text{L2}, x) \ \textbf{and} \ \Sigma.\text{gl}(x) = v \\ & \textbf{and} \ ready_{d,w,t}(\Sigma_d.\text{lockfile}(x)) \ \textbf{then} \\ & \Sigma_d.\text{L2}(x) := (v, \text{CLEAN}, \text{VALID}) \end{aligned}$                                                                    |

| $DeqLoc_{L1}(x)$                                | if $\Sigma_{dw}$ .L1.fifo.tail = $x$<br>and $notDirty(\Sigma_{dw}$ .L1, $x)$ then<br>$\Sigma_{dw}$ .L1.fifo.dequeue()                                                                                                                                                                                                                    |

| $DEQLoc_{L2}(x)$                                | $\begin{aligned} &\textbf{if } \Sigma_d. \text{L2.fifo.tail} = x \\ &\textbf{and } not Dirty(\Sigma_d. \text{L2}, x) \textbf{ then} \\ &\Sigma_d. \text{L2.fifo.dequeue()} \end{aligned}$                                                                                                                                                |

| DEQMARKER <sub>L1</sub>                         | if $\Sigma_{dw}.\text{L1.fifo.tail} = \text{FLUSH then}$<br>$\Sigma_{dw}.\text{L1.fifo.dequeue}()$                                                                                                                                                                                                                                       |

| DEQMARKER <sub>L2</sub>                         | $\begin{aligned} & \textbf{if } \Sigma_d. \text{L2.fifo.tail} = \text{FLUSH } \textbf{then} \\ & \Sigma_d. \text{L2.fifo.dequeue()} \end{aligned}$                                                                                                                                                                                       |

where:

$$notDirty(C, x) \stackrel{\text{def}}{=} (C(x) = \bot) \lor (C(x).\text{hy} = \text{clean})$$

**Table 2.** Environmental transitions

is DIRTY. There is no need to mark the L1 copy as dirty: the value it holds is the same as the value that will be propagated to global memory once the L2 entry (eventually) flushes.

Remark 1 (On caching protocols). We model caches as if each cacheline holds the contents of a single location, but real cachelines hold the contents of several consecutive locations. Therefore, real caches may fetch more than just the requested location; we model this by allowing any location to be fetched at any time. Real caches may flush multiple locations simultaneously, but since they use a dirty bit mask,

it is as if the flush is per-location. Real cacheline locking may restrict access to more locations than our model suggests, but this extra locking can only lead to fewer behaviours, thus making our model sound. The caches used in the evaluated design are *write-through* and *write-allocate* [19: Tab. 1];<sup>5</sup> we safely capture write-through behaviour by allowing the environment to flush at any time, and write-allocate behaviour by having ST create a cache entry if none exists.

# 5.4 Compilation Scheme

We now consider the compilation of OpenCL+RSP programs into the assembly language of §5.2.

Although our assembly language can apply to a multiple-device system, this subsection, in line with the original RSP proposal, considers only the single-device case [19: §5]. This means that our compilation scheme does not extend to OpenCL+RSP operations that use ALL-scope.

The compilation scheme shown in the 'Original' column of Tab. 3 is what we believe to be a faithful representation of the original proposed scheme [19], informed by a series of interviews with the broader set of RSP designers. As a result of our formalisation work, we have found problems with this scheme, which we elucidate in §5.5. We propose instead the compilation scheme shown in the 'Proposed' column of Tab. 3, which addresses these problems. We now explain and justify our proposed scheme; a proof that it is sound follows in §6.

Our explanation centres on how the compilation scheme ensures correct release/acquire semantics (so that inter-workgroup message-passing programs, such as

$$store_{na}(x, 42);$$

|||  $if(r0 = load_{DV,N}(y))$

$store_{DV,N}(y,1);$  ||  $r1 = load_{na}(x);$

can never yield  $\{r0 = 1, r1 = 0\}$ ) and also ensures RMW atomicity (so that programs like the one in Example 3 can never finish with x = 1).

**Loads** An OpenCL load that is non-atomic (na) or at workgroup (WG) scope is compiled to a lone LD instruction **①**. No further instructions are required because consistency need only be enforced as far as the L1 cache, which LD already targets natively. For a load at DV scope **②**, we ensure 'acquire' semantics by invalidating the L1 cache after the LD. This ensures that subsequent loads observe values from the L2 cache.

To upgrade the load to a remote load, the invalidation is preceded by a flush of all the L1 caches in the device **3**; this ensures that subsequent loads observe values that have been written to any L1 cache.

**Stores** As for loads, non-atomic or wg-scope stores are compiled to lone ST instructions **4**. For a store at DV scope, we ensure 'release' semantics by flushing the L1 cache before

| Ope      | enCL+RSP operation                                                                       | Original                                                                                                                                                                                                                                                                                                                                       | Proposed                                                                                                                                                         |

|----------|------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0        | $\begin{array}{l} r = \mathtt{load_{na}}(x) \\ r = \mathtt{load_{WG,\_}}(x) \end{array}$ | $\mathtt{LD}rx$                                                                                                                                                                                                                                                                                                                                | $\mathtt{LD}rx$                                                                                                                                                  |

| <b>9</b> | $r = \mathtt{load}_{\mathtt{DV},\mathtt{N}}(x)$                                          | $\begin{array}{c} {\rm INV_{L1}WG} \\ {\rm LD}rx \end{array}$                                                                                                                                                                                                                                                                                  | $\begin{array}{c} \operatorname{LD} r  x \\ \operatorname{INV_{L1} WG} \end{array}$                                                                              |

| •        | $r = \mathtt{load_{DV,R}}(x)$                                                            | $\begin{array}{c} \operatorname{LK}_{\operatorname{L2}} x \\ \operatorname{FLU}_{\operatorname{L1}} \operatorname{DV} \\ \operatorname{INV}_{\operatorname{L1}} \operatorname{WG} \\ \operatorname{LD} r x \\ \operatorname{UL}_{\operatorname{L2}} x \end{array}$                                                                             | $\begin{array}{c} \operatorname{LD} r  x \\ \operatorname{FLU_{L1}} \operatorname{DV} \\ \operatorname{INV_{L1}} \operatorname{WG} \end{array}$                  |

| 4        | $\texttt{store}_{\texttt{ma}}(x,r) \\ \texttt{store}_{\texttt{WG},\_}(x,r)$              | $\operatorname{ST} r x$                                                                                                                                                                                                                                                                                                                        | $\operatorname{ST} r x$                                                                                                                                          |

| 6        | $\mathtt{store}_{\mathtt{DV},\mathtt{N}}(x,r)$                                           | $\begin{array}{c} \mathtt{FLU_{L1}}  \mathtt{WG} \\ \mathtt{ST}  r  x \end{array}$                                                                                                                                                                                                                                                             | $\begin{array}{c} \operatorname{FLU_{L1}WG} \\ \operatorname{ST} r  x \end{array}$                                                                               |

| 6        | $\mathtt{store}_{\mathtt{DV},\mathtt{R}}(x,r)$                                           | $\begin{array}{c} \operatorname{LK_{L2}} x \\ \operatorname{FLU_{L1}} \operatorname{WG} \\ \operatorname{ST} r x \\ \operatorname{INV_{L1}} \operatorname{DV} \\ \operatorname{UL_{L2}} x \end{array}$                                                                                                                                         | $\begin{array}{c} LK_{rmw}  DV \\ FLU_{L1}  DV \\ INV_{L1}  DV \\ ST  r  x \\ FLU_{L1}  WG \\ INV_{L1}  DV \\ UL_{rmw}  DV \end{array}$                          |

| 0        | $r = \mathtt{fetch\_inc}_{\mathtt{WG},\_}(x)$                                            | $INC_{L1} r x$                                                                                                                                                                                                                                                                                                                                 | ${\tt INC_{L1}}rx$                                                                                                                                               |

| 8        | $r = \mathtt{fetch\_inc}_{\mathtt{DV},\mathtt{N}}(x)$                                    | $\begin{array}{c} \operatorname{FLU_{L1}}\operatorname{WG} \\ \operatorname{INV_{L1}}\operatorname{WG} \\ \operatorname{INC_{L2}}r\ x \end{array}$                                                                                                                                                                                             | $\begin{aligned} & \texttt{FLU}_{\texttt{L1}} \ \texttt{WG} \\ & \texttt{INC}_{\texttt{L2}} \ r \ x \\ & \texttt{INV}_{\texttt{L1}} \ \texttt{WG} \end{aligned}$ |

| 9        | $r = \mathtt{fetch\_inc}_{\mathtt{DV},\mathtt{R}}(x)$                                    | $\begin{array}{c} \operatorname{LK_{rmw}}\operatorname{DV} \\ \operatorname{LK_{L2}} x \\ \operatorname{FLU_{L1}}\operatorname{DV} \\ \operatorname{INV_{L1}}\operatorname{WG} \\ \operatorname{INC_{L2}} r x \\ \operatorname{INV_{L1}}\operatorname{DV} \\ \operatorname{UL_{L2}} x \\ \operatorname{UL_{rmw}}\operatorname{DV} \end{array}$ | $\begin{array}{c} LK_{rmw}  DV \\ FLU_{L1}  DV \\ INV_{L1}  DV \\ INC_{L2}  r  x \\ FLU_{L1}  DV \\ INV_{L1}  DV \\ UL_{rmw}  DV \end{array}$                    |

**Table 3.** Compilation schemes, original and proposed

the ST. This ensure that prior stores are visible to operations that subsequently read from the L2 cache **6**.

To upgrade to a remote store  $\mathfrak{G}$ , we must also ensure that prior stores are visible to operations that subsequently read from their own L1 cache. For this, we precede the ST instruction with a remote invalidate (INV<sub>L1</sub> DV). The other instructions are present to ensure that any wg-scoped increments, simultaneously executing on different work-group, are performed atomically. Without them, we might observe such violations of RMW atomicity as were seen earlier in Example 2. Naturally, these increments cannot happen between the LK<sub>rmw</sub> and UL<sub>rmw</sub> instructions. In case one happens *before* the LK<sub>rmw</sub>, we use a remote flush (FLU<sub>L1</sub> DV) to ensure that it is promptly flushed, and thus unable to overwrite our upcoming store. In case one happens *after* the UL<sub>rmw</sub>, we use a local

<sup>&</sup>lt;sup>5</sup> The original RSP description reported the caches as being *write-no-allo-cate*, but we confirm that this was in error.

flush and a remote invalidate after our store, to ensure that the increment will observe our stored value.

Atomic increments We map the atomic fetch-and-increment operation, fetch\_inc, to the INC assembly instruction. At WG scope, the INC operation acts on the L1 cache ②, and at DV scope, it acts directly on the L2 cache ③. Performing the operation directly on the L2 cache (rather than on the L1 cache and then flushing) ensures the atomicity of RMW operations. Moreover, at DV scope, the fetch\_inc must provide acquire+release semantics. Accordingly, it begins with a flush (inherited from the release store, ⑤) and finishes with an invalidate (inherited from the acquire load, ②).

Upgrading to a remote increment imposes several requirements **②**. To ensure acquire semantics, the remote increment must end with (at least) a remote-flush and a local-invalidate (as for the remote load discussed above). To ensure release semantics, it must begin with (at least) a local-flush and a remote-invalidate (as for the remote store). For RMW atomicity, it must observe any concurrent increments on another L1 cache that occur before the RMW lock is acquired, and any that happen after the RMW lock is released must observe the newly-incremented value. Therefore, the remote increment must begin with (at least) a remote-flush and a local-invalidate, and end with (at least) a local-flush and a remote-invalidate. Merging all these constraints together, we find remote flushes and invalidates are required both before and after the INC<sub>L2</sub>.

# 5.5 Problems with the Original Scheme

We describe two errors in the original compilation scheme (Tab. 3, 'Original' column), and explain how our proposed scheme ('Proposed' column) addresses them. Finding these issues early in the design process is, we believe, the key value of formalisation efforts such as ours.

#### 5.5.1 Non-Remote Loads Can Violate Message-Passing

Because DV-scoped non-remote loads (② in Tab. 3) invalidate their L1 cache *before* the LD [19: §2.3], coherence (axiom Coh in Fig. 2) is violated. To explain this, Fig. 4 exhibits a machine execution, obtained by compiling a basic inter-work-group message-passing idiom, that leads to a prohibited final state. The vertical order in the figure illustrates the interleaving of each thread's instructions and environment transitions, and we include frequent snapshots of the machine's state. In braces, we show the cache entries (using C = CLEAN, D = DIRTY, V = VALID, and I = INVALID), and in brackets we show the contents of non-empty synchronisation fifos. Since our compilation scheme covers only the single device case, we treat the shared L2 cache as if it is global memory.

Initially, all memory is zeroed and all caches are empty. If r0 observes 1, then coherence on x dictates that r1 must observe 42. Thread 2 invalidates its L1 cache, but then the environment immediately repopulates it with x's initial value. Thread 1 (which, being in a different work-group, has its own

| Thread 1 (executing                                                                                                                                | L2 cache                                                                                                     | Thread 2 (executing                                                                                                    |

|----------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------|