# The Design and Implementation of a Verification Technique for GPU Kernels

ADAM BETTS, NATHAN CHONG, ALASTAIR F. DONALDSON, and JEROEN KETEMA, Imperial College London

SHAZ QADEER, Microsoft Research Redmond

PAUL THOMSON and JOHN WICKERSON, Imperial College London

We present a technique for the formal verification of GPU kernels, addressing two classes of correctness properties: data races and barrier divergence. Our approach is founded on a novel formal operational semantics for GPU kernels termed *synchronous*, *delayed visibility* (SDV) semantics, which captures the execution of a GPU kernel by multiple groups of threads. The SDV semantics provides operational definitions for barrier divergence and for both inter- and intra-group data races. We build on the semantics to develop a method for reducing the task of verifying a massively parallel GPU kernel to that of verifying a sequential program. This completely avoids the need to reason about thread interleavings, and allows existing techniques for sequential program verification to be leveraged. We describe an efficient encoding of data race detection and propose a method for automatically inferring the loop invariants that are required for verification. We have implemented these techniques as a practical verification tool, GPUVerify, that can be applied directly to OpenCL and CUDA source code. We evaluate GPUVerify with respect to a set of 162 kernels drawn from public and commercial sources. Our evaluation demonstrates that GPUVerify is capable of efficient, automatic verification of a large number of real-world kernels.

Categories and Subject Descriptors: F.3.1 [Logics and Meanings of Programs]: Specifying and Verifying and Reasoning about Programs

General Terms: Theory, Verification

Additional Key Words and Phrases: Verification, GPUs, concurrency, data races, barrier synchronization

#### **ACM Reference Format:**

Adam Betts, Nathan Chong, Alastair F. Donaldson, Jeroen Ketema, Shaz Qadeer, Paul Thomson, and John Wickerson. 2015. The design and implementation of a verification technique for GPU kernels. ACM Trans. Program. Lang. Syst. 37, 3, Article 10 (May 2015), 49 pages.

DOI: http://dx.doi.org/10.1145/2743017

## 1. INTRODUCTION

In recent years, massively parallel *accelerator* processors, primarily graphics processing units (GPUs) from companies such as AMD, Nvidia, and ARM, have become widely available to end users. Accelerators offer significant compute power at a low cost,

This work was supported by the EU FP7 STREP project CARP (project number 287767), by EPSRC project EP/G051100/2, and by two EPSRC-funded PhD studentships. Part of the work was carried out while Alastair Donaldson was a Visiting Researcher at Microsoft Research Redmond. This article is a revised and extended version of Betts et al. [2012].

Authors' addresses: A. Betts, N. Chong, A. F. Donaldson, J. Ketema, P. Thomson, and J. Wickerson, Department of Computing, Imperial College London, 180 Queen's Gate, London SW7 2BZ, United Kingdom; emails: {a.betts, n.chong10, alastair.donaldson, j.ketema, paul.thomson11, j.wickerson}@imperial.ac.uk; S. Qadeer, Microsoft Research, One Microsoft Way, Redmond, WA 98052, USA; email: qadeer@microsoft.com.

Permission to make digital or hard copies of part or all of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that copies show this notice on the first page or initial screen of a display along with the full citation. Copyrights for components of this work owned by others than ACM must be honored. Abstracting with credit is permitted. To copy otherwise, to republish, to post on servers, to redistribute to lists, or to use any component of this work in other works requires prior specific permission and/or a fee. Permissions may be requested from Publications Dept., ACM, Inc., 2 Penn Plaza, Suite 701, New York, NY 10121-0701 USA, fax +1 (212) 869-0481, or permissions@acm.org.

© 2015 ACM 0164-0925/2015/05-ART10 \$15.00

DOI: http://dx.doi.org/10.1145/2743017

10:2 A. Betts et al.

and algorithms in domains such as medical imaging [Cates et al. 2004], computer vision [Salas-Moreno et al. 2013], computational fluid dynamics, [Harris 2004] and DNA sequence alignment [Li and Durbin 2009; Klus et al. 2012] can be accelerated to beat CPU performance, sometimes by orders of magnitude. Importantly, GPUs enable performance improvements not only in terms of runtime but also in terms of energy efficiency [Lokhmotov 2011].

GPUs present a serious challenge for software developers. A system may contain one or more of the plethora of devices on the market. Applications must exhibit *portable correctness*, operating correctly on any GPU accelerator. Software bugs in media, entertainment, and business domains can have serious financial implications, and bugs in safety critical domains, such as medical applications, can be more drastic still. Because GPUs are being used increasingly in such areas, there is an urgent need for verification techniques to aid the construction of correct GPU software.

In this work, we address the problem of static verification of GPU kernels written using mainstream programming models such as OpenCL [Khronos OpenCL Working Group 2012], CUDA [Nvidia 2012a], and C++ AMP [Microsoft Corporation 2012]. We focus on two classes of bugs that make writing correct GPU kernels harder than writing correct sequential code: *data races* and *barrier divergence*.

In contrast to the well-understood notion of data races, there does not appear to be a formal definition of barrier divergence for GPU programming. Our work gives a precise characterization of barrier divergence via an operational semantics based on predicated execution, which we call *synchronous*, *delayed visibility (SDV)* semantics. The SDV semantics models the execution of a kernel by multiple groups of threads, and provides operational definitions for inter- and intra-group data races as well as barrier divergence. While predicated execution has been used for code generation by GPU kernel compilers, our work is the first to use predicated operational semantics for the purpose of specification and verification.

Founded on the SDV semantics, we present a verification method which transforms a massively parallel GPU kernel into a sequential program such that correctness of the sequential program implies data race- and barrier divergence-freedom of the kernel. Our method achieves scalability by exploiting the fact that data races and barrier divergence are *pairwise* properties, allowing a reduction to an arbitrary pair of threads. For this reduction to be sound, it is necessary to use abstraction to model the possible effects of other threads. We consider two practical abstraction methods, the *adversarial* abstraction and the more refined *equality* abstraction, and prove formally that the reduction to a pair of threads is sound when combined with these abstractions.

Reducing the analysis of a highly concurrent program to the verification of a sequential program completely avoids the need to reason about thread interleavings, and enables reuse of existing verification techniques for sequential programs. We present novel heuristics for automatically inferring loop invariants required for verification.

We discuss the design and implementation of GPUVerify, a practical tool for verifying GPU kernels using our method, which can be applied directly to OpenCL and CUDA source code. GPUVerify builds on the Clang/LLVM compiler infrastructure<sup>1</sup>, the Boogie verification system [Barnett et al. 2005] and the Z3 theorem prover [de Moura and Bjørner 2008].

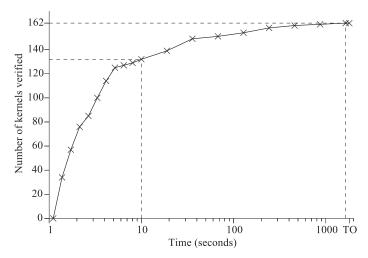

We have used GPUVerify to analyze a set of 162 OpenCL and CUDA kernels. We summarize an experiment with the initial implementation of GPUVerify (which was limited to intragroup race checking [Betts et al. 2012]) where we divided these kernels into separate *training* and *evaluation* sets, tuned the capabilities of the tool to the training set, and then ran the tool *blindly* on the evaluation set (none of our team

<sup>&</sup>lt;sup>1</sup>http://clang.llvm.org/.

were familiar with the kernels in the evaluation set). We found that fully automatic verification was achieved for 49 out of 70 kernels from the evaluation set (69%). We also present a comparison of the initial GPUVerify implementation with PUG, a formal analysis tool for CUDA kernels by Li and Gopalakrishnan [2010]. GPUVerify performs competitively with PUG when verifying correct kernels and rejects defective kernels in several cases where PUG reports false negatives. Additionally, the equality abstraction offered by GPUVerify is more refined than the shared state abstraction supported by PUG, allowing verification of real-world kernels for which PUG reports false positives.

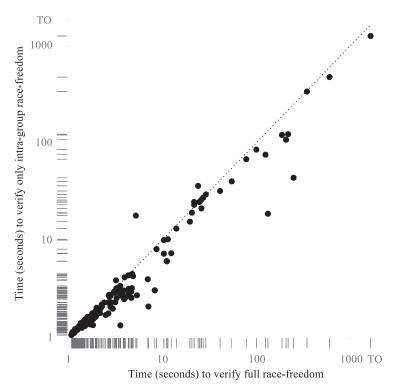

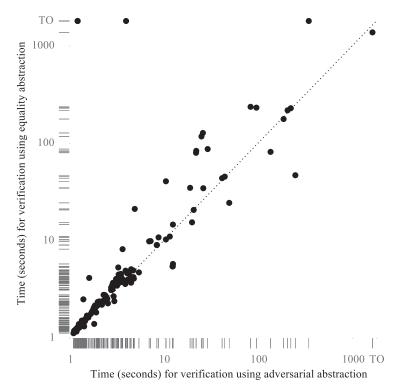

We also report on a more recent version of GPUVerify, which supports intergroup race checking, to analyze our benchmarks, using a combination of improved invariant inference and manual invariant annotations to achieve verification across the entire benchmark set. We report on the performance of GPUVerify, assess the overhead associated with performing intergroup race checking on top of intragroup race checking, and compare the performance and precision of GPUVerify when the adversarial versus equality abstractions are used.

In summary, our article makes the following contributions:

- —Synchronous, delayed visibility (SDV) semantics: a formal operational semantics for GPU kernels based on predicated execution, inter- and intragroup data-race freedom, and barrier divergence freedom.

- —The *two-thread reduction*: an abstract version of the SDV semantics that models a pair of threads, and a soundness theorem showing that data race- and barrier divergence-freedom of a massively parallel kernel according to the SDV semantics can be established by proving data race- and barrier divergence-freedom for each pair of threads using the abstract semantics.

- —A verification method for GPU kernels which exploits the SDV semantics and twothread reduction to transform analysis to a sequential program verification task, allowing reuse of existing analysis techniques based on verification condition generation and automated theorem proving.

- —A method for automatically inferring the invariants needed for our verification method.

- —An extensive evaluation of our verifier on a collection of 162 publicly available and commercial GPU kernels.

#### **Contributions in Relation to Prior Work**

We make explicit how the current article significantly extends a previous conference version [Betts et al. 2012] and complements other papers that have arisen from the GPUVerify project [Collingbourne et al. 2013; Chong et al. 2013; Bardsley and Donaldson 2014; Bardsley et al. 2014a; Chong et al. 2014].

Treatment of Multigroup GPU Kernels. The original presentation of our verification method was restricted to the analysis of single-group GPU kernels. Here we treat the multigroup case by extending the formal semantics for kernels, implementing intergroup race checking in the GPUVerify tool, and conducting an experimental evaluation to assess the overhead associated with handling multiple groups versus just a single group.

A Full Soundness Proof for the Two-Thread Reduction. The scalability of our verification method hinges on reducing the analysis to consider an arbitrary pair of threads. Only a short proof sketch for the soundness of this "two-thread reduction" was presented in our prior work. In the current article, we present, for the first time, a detailed formal soundness proof. This is an important contribution because a similar reduction is also employed by other methods, such as the PUG verifier of Li and Gopalakrishnan [2010].

10:4 A. Betts et al.

Mechanical Checking of the Language and Semantics Definitions. We have used the Isabelle proof assistant to type check all the definitions, semantic rules, and theorem statements appearing in the article. The result is published in the Archive of Formal Proofs [Wickerson 2014]. We have also conducted a partial mechanization of the soundness proof for the two-thread reduction.

New Experimental Evaluation. Rather than repeating the extensive experimental evaluation presented in our prior work [Betts et al. 2012], we instead summarize the results of this evaluation and present a new evaluation in which we assess the verification performance of a more recent version of the GPUVerify tool, as well as evaluating the overhead associated with intergroup race checking and performance characteristics of two-shared state abstractions used by the tool.

Relation to Other Papers Arising from the GPUVerify Project. In addition to the original version of the article [Betts et al. 2012], we have published three technical articles that extend the GPUVerify verification method, each in a distinct manner [Collingbourne et al. 2013; Chong et al. 2013; Bardsley and Donaldson 2014]. Each of these extensions is separate from—and complementary to—the new contributions made in the current article.

Following our prior work [Betts et al. 2012], the results presented in this article apply to structured GPU kernels expressed using **if** and **while** constructs. In related work, we have generalized the lock-step execution semantics used by our method to apply to unstructured control flow graphs, allowing the technique to be applied at the level of the intermediate representation used by a compiler [Collingbourne et al. 2013].

We have proposed *barrier invariants* [Chong et al. 2013] as a mechanism to allow users to improve on the precision offered by the *adversarial* and *equality* abstractions used in this work. The shared state abstractions discussed here are straightforward to apply automatically, but are inflexible. Barrier invariants are instead provided by a user; they offer a tunable, but heavyweight and manually driven, approach to GPU kernel verification.

These works, like the current contribution, are restricted to a barrier synchronizing programming model. We have conducted a preliminary investigation into lifting the method beyond this model to cater for kernels in which threads communicate using atomic operations and warp-based synchronization [Bardsley and Donaldson 2014].

As well as technical articles that extend the core verification method, a recent tool paper discusses engineering experience and insight gained during the GPUVerify project [Bardsley et al. 2014a], and an invited article provides a tutorial overview of the technique [Donaldson 2014]. We have also applied GPUVerify as a component in an automatic verification method for parallel prefix sum kernels [Chong et al. 2014].

## Reproducibility

The GPUVerify tool is open source and available online at http://multicore.doc.ic.ac.uk/tools/GPUVerify.

On the tool web page we make available the versions of GPUVerify used for the experiments reported in this paper, together with the non-commercial benchmarks used for our evaluation.

## 2. GPU KERNEL PROGRAMMING

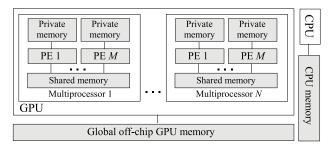

A typical GPU (see Figure 1) consists of a large number of simple *processing elements* (*PEs*), sometimes referred to as *cores*. Subsets of the PEs are grouped together into *multiprocessors*, such that all PEs within a multiprocessor execute in lock-step, in single instruction multiple data (SIMD) fashion. Distinct multiprocessors on a GPU

Fig. 1. Schematic overview of a typical GPU architecture.

Table I. Equivalent Terms for What We Shall Call *private*, *shared*, and *global* Memory in CUDA, OpenCL, and C++ AMP

| Term    | CUDA   | OpenCL  | C++ AMP     |

|---------|--------|---------|-------------|

| private | local  | private | local       |

| shared  | shared | local   | tile static |

| global  | global | global  | global      |

can execute independently. Each PE is equipped with a small private memory, and PEs located on the same multiprocessor can access a portion of *shared* memory dedicated to that multiprocessor. All PEs on the GPU have access to a large amount of off-chip memory known as *global* memory, which is usually separate from main CPU memory.

Today, there are three major GPU programming models: OpenCL, an industry standard proposed by the Khronos OpenCL Working Group [2012] and widely supported (in particular, OpenCL is AMD's primary high-level GPU programming model); CUDA, from Nvidia [2012a]; and C++ AMP, from Microsoft [2012]. Table I summarizes the terms used in the programming models to refer to *private*, *shared*, and *global* memory.

Threads and Groups. All three programming models provide a similar high-level abstraction for mapping computation across GPU hardware, centered around the notion of a kernel program being executed by many parallel threads, together with a specification of how these threads should be partitioned into groups. The kernel is a template specifying the behavior of an arbitrary thread, parameterized by thread and group ID variables. Expressions over these IDs allow distinct threads to operate on separate data and follow differing execution paths through the kernel. Threads in the same group can synchronize during kernel execution, while threads in distinct groups execute completely independently.

The runtime environment associated with a GPU programming model must interface with the driver of the available GPU to schedule execution of kernel threads across processing elements. Typically each group of threads is assigned to one of the multiprocessors of the GPU, so that distinct groups execute in parallel on different multiprocessors. If the number of threads in a group is N and the number of PEs in a multiprocessor is M, then a group is divided into  $\lceil \frac{N}{M} \rceil$  subgroups, each consisting of up to M threads. Execution of a single group on a multiprocessor then proceeds by scheduling the subgroups in an interleaving manner. Each thread in a given subgroup is pinned to a distinct PE, and all threads in the same subgroup execute together in lock-step, following exactly the same control path. Distinct subgroups may follow different control paths.

Table II summarizes the specific terms used by the three main GPU programming models to refer to *threads*, *groups*, and (in the case of CUDA), *subgroups*. OpenCL and C++ AMP aim for portability across GPUs from multiple vendors, so they do not allow

10:6 A. Betts et al.

Table II. Equivalent Terms for thread, group, and (Where Applicable) subgroup in CUDA,

OpenCL, and C++ AMP

| Term      | CUDA         | OpenCL     | C++ AMP |

|-----------|--------------|------------|---------|

| thread    | thread       | work-item  | thread  |

| group     | thread block | work-group | tile    |

| sub-group | warp         | N/A        | N/A     |

Table III. Predicated forms for Conditionals and Loops

| Program fragment          | Predicated form                                    |

|---------------------------|----------------------------------------------------|

| <pre>if(lid &gt; N)</pre> | p = (lid > N);                                     |

| x = 0;                    | $p \Rightarrow x = 0;$<br>$! p \Rightarrow x = 1;$ |

| else                      |                                                    |

| x = 1;                    |                                                    |

|                           | p = (i < x);                                       |

| while (i < x) $\{$        | while $(\exists t :: t.p)$ {                       |

| i++;                      | $p \Rightarrow i++;$                               |

| }                         | $p \Rightarrow p = (i < x);$                       |

|                           | }                                                  |

a kernel to query the device-specific size or structure of thread subgroups.<sup>2</sup> As CUDA is Nvidia-specific, CUDA programmers *can* write kernels that make assumptions about the division of threads into subgroups. However, such kernels will not easily port to general-purpose GPU programming languages and may break when executed on future generations of Nvidia hardware using a different subgroup size. Thus, GPU kernels that do not make assumptions about the size of thread subgroups are preferable.

*Predicated Execution*. Recall that the PEs in a GPU multiprocessor execute in lock-step, such as a SIMD processor array. Threads within a subgroup occupy the PEs of a multiprocessor, and thus must also execute in lock-step. Conditional statements and loops through which distinct threads in the same subgroup should take different paths must, therefore, be simulated, and this is achieved using *predicated execution*.

Consider the conditional statement in the top left of Table III, where lid denotes the local ID of a thread within its group and x is a local variable stored in private memory. This conditional can be transformed into the straight-line code shown in the top right of the figure, which can be executed by a subgroup in lock-step. The meaning of a statement  $predicate \Rightarrow command$  is that a thread should execute command if predicate holds for that thread; otherwise, the thread should execute a no-op. All threads evaluate the condition lid > N into a local Boolean variable p, then execute both the then and else branches of the conditional, predicated by p and !p, respectively.

Loops are turned into predicated form by dictating that all threads in a subgroup continue to execute the loop body until the loop condition is false for *all* threads in the subgroup, with threads for whom the condition does not hold becoming disabled. This is illustrated for the loop in the bottom left of Table III (where i and x are local variables) by the code fragment shown in the bottom right of the figure. First, the condition i < x is evaluated into local variable p. Then the subgroup loops while p remains true for some thread in the subgroup, indicated by  $\exists$  t::t.p. The loop body is predicated by p, and thus has an effect only for enabled threads.

We present precise operational semantics for predicated execution in Section 3.

*Barrier Synchronization*. When a thread  $t_1$  writes to an address in shared or global memory, the result of this write is not guaranteed to become visible to another thread

<sup>&</sup>lt;sup>2</sup>The recent OpenCL 2.0 extension specification [Khronos OpenCL Working Group 2014b, Section 9.17, p. 133] contains an optional extension to support subgroups of threads.

$t_2$  unless  $t_1$  and  $t_2$  synchronize. As noted earlier, there is no mechanism for threads in distinct groups to synchronize during kernel execution.<sup>3</sup> Threads in the same group can synchronize via barriers. Intuitively, a kernel thread belonging to group g waits at a barrier statement until every thread in g has reached the barrier. Passing the barrier guarantees that all writes to shared and global memory by threads in g occurring before execution of the barrier have been committed.

Our analysis through writing GPU kernels and talking to GPU developers is that there are two specific classes of bugs that make writing correct GPU kernels more difficult than writing correct sequential code: *data races* and *barrier divergence*.

#### 2.1. Data Races

We distinguish between two kinds of data races in GPU kernels. An *intergroup data* race occurs if there are two threads  $t_1$  and  $t_2$  from different groups such that  $t_1$  writes to a location in global memory and  $t_2$  writes to or reads from this location. An *intragroup data race* occurs if there are two threads  $t_1$  and  $t_2$  from the same group such that  $t_1$  writes to a location in global or shared memory,  $t_2$  writes to or reads from this location, and no barrier statement is executed between these accesses. Races can lead to nondeterministic kernel behavior and computation of incorrect results.

## 2.2. Barrier Divergence

If threads in the same group *diverge*, reaching different barriers as in the following kernel fragment:

```

if ((lid%2) == 0)

barrier();  //Even threads hit first barrier

else

barrier();  //Odd threads hit second barrier

```

then kernel behavior is undefined. According to CUDA [Nvidia 2012a]:

"execution is likely to hang or produce unintended side effects."

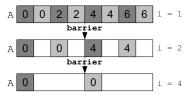

While there is clarity across all programming models as to the meaning of barrier divergence in loop-free code, the situation is far from clear for code with loops. Consider the example kernel shown on the left of Figure 2. This kernel is intended to be executed by one group of four threads, and declares an array A of two shared buffers, each of size four. Private variable buf is an index into A, representing the *current* buffer. The threads execute a nest of loops. On each inner loop iteration, a thread reads the value of the current buffer at index lid+1 modulo 4 and writes the result into the noncurrent buffer at index lid. A barrier is used to avoid data races on A. Notice that local variables x and y are set to 4 and 1, respectively, for thread 0, and to 1 and 4, respectively, for all other threads. As a result, we expect thread 0 to perform four outer loop iterations, each involving one inner loop iteration, while other threads will perform a single outer loop iteration, consisting of four inner loop iterations.

According to the guidance in the CUDA documentation, such a kernel appears to be valid: all threads will hit the barrier statement four times. Taking a snapshot of the array A at each barrier and at the end of the kernel, we might expect to see the

<sup>&</sup>lt;sup>3</sup>In OpenCL 2.0, limited forms of interworkgroup synchronization can be implemented using atomic operations [Khronos OpenCL Working Group 2014a]. However, an interworkgroup barrier still cannot be reliably implemented due to lack of progress guarantees between groups.

10:8 A. Betts et al.

```

shared int A[2][4];

void kernel() {

p = (i < x);

int buf, x, y, i, j;

while (\exists t::t.p) {

x = (lid == 0 ? 4 : 1);

p \Rightarrow j = 0;

y = (1id == 0 ? 1 : 4);

q = p \&\& (j < y);

buf = i = 0;

while (\exists t::t.q) {

while (i < x) {

q ⇒ barrier();

\dot{j} = 0;

q \Rightarrow A[1-buf][lid]

while (j < y) {

= A[buf][(lid+1)%4];

barrier();

q \Rightarrow buf = 1 - buf;

A[1-buf][lid]

q \Rightarrow j++;

= A[buf][(lid+1)%4];

q \Rightarrow q = p \&\& (j < y);

buf = 1 - buf;

j++;

p \Rightarrow i++;

p \Rightarrow p = (i < x);

i++;

}

}

```

Fig. 2. Illustration of the subtleties of barriers in nested loops.

following:

```

A = \{\{0, 1, 2, 3\}, \{-, -, -, -\}\} \rightarrow \{\{0, 1, 2, 3\}, \{1, 2, 3, 0\}\} \rightarrow \{\{2, 3, 0, 1\}, \{1, 2, 3, 0\}\} \rightarrow \{\{2, 3, 0, 1\}, \{3, 0, 1, 2\}\} \rightarrow \{\{0, 1, 2, 3\}, \{3, 0, 1, 2\}\},

```

under the assumption that, during each inner loop iteration, threads 1, 2, and 3 wait at the barrier until thread 0 reaches the barrier again by proceeding to the next iteration of the outer loop.

However, consider the predicated version of the kernel shown in part on the right of Figure 2. This is the form in which the kernel executes on an Nvidia GPU. The four threads comprise a single subgroup. All threads will enter the outer loop and execute the first inner loop iteration. Then thread 0 will become disabled (q becomes *false*) for the inner loop. Thus, the barrier will be executed with some, but not all, threads in the subgroup enabled. On Nvidia hardware, a barrier is compiled to a bar.sync instruction in the PTX (Parallel Thread Execution) assembly language. According to the PTX documentation [Nvidia 2012b],

"if any thread in a [subgroup] executes a bar instruction, it is as if all the threads in the [subgroup] have executed the bar instruction."

Thus, threads 1, 2, and 3 will not wait at the barrier until thread 0 returns to the inner loop: they will simply continue to execute past the barrier, performing three more inner loop iterations. In effect, thread 0 is disabled, while threads 1, 2, and 3 perform these additional loop iterations, because in practice the threads execute in lock step. This yields the following sequence of state-changes to *A*:

```

A = \{\{0, 1, 2, 3\}, \{-, -, -, -\}\} \rightarrow \{\{0, 1, 2, 3\}, \{1, 2, 3, 0\}\} \rightarrow \{\{0, 3, 0, 1\}, \{1, 2, 3, 0\}\} \rightarrow \{\{0, 3, 0, 1\}, \{1, 0, 1, 0\}\} \rightarrow \{\{0, 1, 0, 1\}, \{1, 0, 1, 0\}\}.

```

Table IV. The Litmus Test of Figure 2 Yields a Range of Results across Varying Platforms

| Architecture       | Final state of A                                                                                                                                           |

|--------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Nvidia Tesla C2050 | $\{\{0, 1, 0, 1\}, \{1, 0, 1, 0\}\}$                                                                                                                       |

| AMD Tahiti         | $\{\{0, 1, 2, 3\}, \{1, 2, 3, 0\}\}$                                                                                                                       |

| ARM Mali-T600      | $\{\{0, 1, 2, 3\}, \{3, 0, 1, 2\}\}$                                                                                                                       |

| Intel Xeon X5650   | $ \begin{aligned} &\{\{0,1,0,1\},\{1,0,1,0\}\}\\ &\{\{0,1,2,3\},\{1,2,3,0\}\}\\ &\{\{0,1,2,3\},\{3,0,1,2\}\}\\ &\{\{*,*,*,1\},\{3,0,1,2\}\} \end{aligned}$ |

After the inner loop exits, thread 0 becomes enabled, but all other threads become disabled, for a further three outer loop iterations, during each of which thread 0 executes a single inner loop iteration. The state of A thus remains  $\{\{0, 1, 0, 1\}, \{1, 0, 1, 0\}\}$ .

The OpenCL standard [Khronos OpenCL Working Group 2012] gives a better, though still informal definition, stating:

"If barrier is inside a loop, all [threads] must execute the barrier for each iteration of the loop before any are allowed to continue execution beyond the barrier,"

which at least can be interpreted as rejecting the example of Figure 2.

To investigate this issue in practice, we implemented the litmus test of Figure 2 in both CUDA and OpenCL and (with help from contacts in the GPU industry; see Acknowledgments) ran the test on GPU architectures from Nvidia, AMD and ARM, and on an Intel Xeon CPU (for which there is an OpenCL implementation). Our findings are reported in Table IV. Observe that the test result does not agree between any two vendors. The Nvidia results match our earlier prediction. The AMD result also appears to stem from predicated execution. ARM's Mali architecture does *not* use predicated execution [Lokhmotov 2011], so perhaps unsurprisingly gives the 'intuitive' result we might expect. For Intel Xeon, we found that different threads reported different values for certain array elements in the final shared state, indicated by asterisks in Table IV, which we attribute to cache effects.

The example of Figure 2 is contrived to be small enough to explain concisely and examine exhaustively. It does, however, illustrate that barrier divergence is a subtle issue, and that nonobvious misuse of barriers can compromise correctness and lead to implementation-dependent results. Clearly, a more rigorous notion of barrier divergence is required than the informal descriptions found in the CUDA and OpenCL documentation.

We give a precise, operational definition for barrier divergence in Section 3 which clears up this ambiguity. In essence, our definition states that if a barrier is encountered by a group of threads executing in lock-step under a predicate, the predicate must hold *uniformly* across the group, i.e., the predicate must be *true* for all threads, or *false* for all threads. This precise definition facilitates formal verification of barrier divergence-freedom and is incorporated in the GPUVerify tool we present in Section 5. GPUVerify can accurately analyze the kernel of Figure 2, flagging the barrier divergence issue.

#### 3. OPERATIONAL SEMANTICS FOR GPU KERNELS

Our aim is to verify data race- and barrier divergence-freedom for GPU kernels. ITo do this, we require an operational semantics for GPU kernels that specifies precisely the conditions under which data races and barrier divergence occur.

For checking barrier divergence, the least conservative assumption we can safely make is that a thread group consists of a single subgroup, so that all threads in a group execute in lock-step. Thus, when analyzing barrier divergence-freedom for a kernel in which each thread group consists of N threads, we assume for the purposes of analysis that the subgroup size is also N (so that each thread group trivially contains just one subgroup), regardless of the subgroup size associated with any particular architecture.

10:10 A. Betts et al.

We can then define barrier divergence to occur if and only if the lock-step thread group executes a barrier and the threads are not uniformly enabled: the current predicate of execution holds for some threads but not others. Clearly, if we can prove barrier divergence-freedom for a kernel under this strong assumption of lock-step behavior, the kernel will be free from barrier divergence if thread groups are divided into subgroups at a finer level of granularity.

For example, when analyzing barrier divergence for a kernel in which thread blocks have size 1,024, we assume that the threads execute in lock-step as a single subgroup size of 1,024. Recent GPUs from AMD, Nvidia, and ARM exhibit subgroup sizes of 64, 32, and 1, respectively [AMD 2013; Nvidia 2012a; Lokhmotov 2011]. Our worst-case assumption thus caters for the AMD scenario with the largest subgroup size, as well as the smaller subgroup sizes exhibited by Nvidia and ARM GPUs. Furthermore, the conservative assumption also caters for possible subgroup sizes associated with any other (present or future) architectures.

For race checking, the scenario is reversed: the least conservative safe assumption is that threads in the same group interleave completely asynchronously between pairs of barriers, with no guarantees as to the relative order of statement execution between threads (so that essentially every subgroup consists of just a single thread). This is the case, for example, on ARM's Mali GPU architecture [Lokhmotov 2011]. Clearly, if race-freedom can be proved under this most general condition, then a kernel will remain race-free if, in practice, certain threads in a group execute synchronously.

We propose a semantics that we call *synchronous*, *delayed visibility (SDV)*. Under SDV, group execution is *synchronous*, allowing precise barrier divergence checking. The shared memory accesses of all threads are logged, and when a thread writes to shared memory, the visibility of this write to other threads in the group is *delayed* until the group reaches a barrier. Delaying the visibility of writes ensures that threads do not see a synchronized view of shared and global memory between barriers, catering for the fact that execution might not *really* be fully synchronous. Logging accessed locations allows racing accesses to be detected. The SDV semantics does *not* attempt to directly capture the manner in which threads execute on real GPU architectures which exhibit a mixture of synchronous and interleaving execution in practice; instead, the semantics provides a basis for proving data race- and barrier divergence-freedom.

To describe the SDV semantics formally, we define the *Kernel Programming Language (KPL)*, which captures the essential features of mainstream languages for writing GPU kernels such as CUDA and OpenCL.

## 3.1. Syntax

The syntax for KPL is shown in Figure 3. A KPL kernel declares the number of groups (**groups**: number) and the number of threads in each group (**threads**: number) that will execute the kernel. Thus, the total number of threads that will execute the kernel is equal to the number of declared groups multiplied by the number of declared threads. The group and thread declarations are followed by a list of procedure declarations and a **main** statement. Each procedure has a name, a single parameter, and a body; for brevity, we do not model multiple parameters or return values.

For simplicity, but without loss of generality, threads have access to a single shared array sh, which we refer to as  $global\ memory$ . We make no distinction between shared and global memory (cf. Figure 1) in our programming language; from a verification perspective, it suffices to view shared memory as being part of global memory (by employing the IDs of groups in the calculation of memory addresses). We assume that every local variable and each indexable element of global memory has type Word, the type of memory words. Any value of type Word can be interpreted as an integer or a

Fig. 3. Syntax for Kernel Programming Language.

Boolean. In practice, Word will also represent floating point numbers; structured data will be represented by sequences of values of type Word.

Local expressions are built from constant literals, locations, and the built-in variables *lid* and *gid*, which refer to the local ID of a thread within its group and the ID of the group in which the thread occurs, respectively. Compound expressions are build using an unspecified set of binary operators; the syntax could easily be extended to accommodate operators of other arities.

A thread may update one of its local variables by performing a local computation (v := e, where e is a local expression) or by reading from global memory (v := sh[e], where e is a local expression determining which index to read from). A thread may also update global memory  $(sh[e_1] := e_2, \text{ where } e_1, e_2 \text{ are expressions over local variables, with } e_1 \text{ determining which index to write to, and } e_2 \text{ the value to be written})$ . For simplicity, we assume that all local variables are scalar.

Compound statements are constructed via sequencing, conditional branches, local variable introduction, loops, and procedure calls in the standard way. KPL provides a number of other statements: **barrier**, which is used to synchronize threads in a group; **break**, which causes execution to break out of the closest enclosing loop; **continue**, which causes execution to jump to the head of the closest enclosing loop; and **return**, which causes execution to return from the closest enclosing procedure call.

Figure 3 specifies two syntactic elements that should *not* appear directly in a KPL program; they are used in the semantic rules of Figure 6 which we will explain in Section 3.2. These are: a special  $\underline{\mathbf{while}}$  statement, used to model the dynamic semantics of while loops in which we have to distinguish between the first and subsequent iterations of a loop, and a set V of locations from which storage for local variables is allocated as they come into scope dynamically.

We assume that programs are well formed according to the usual rules, e.g., statements should only refer to declared variables, and variable introduction should not

10:12 A. Betts et al.

hide a variable introduced earlier in an enclosing scope. In addition, we require the main statement not to contain a **return**; this nonconsequential restriction simplifies our presentation somewhat (it avoids having to apply the function *relim* of Figure 6, discussed in Section 3.2, to the main statement).

We do not formalize features of GPU kernels such as multidimensional groups and arrays. However, our verification method and implementation, described in Section 5, handles both.

#### 3.2. Semantics

Given a function  $f:A\to B$  and elements  $a\in A,b\in B$ , we write  $f[a\mapsto b]$  to denote the function  $g:A\to B$  such that g(x)=f(x) for all  $x\in A\setminus\{a\}$ , and g(a)=b otherwise. We abbreviate  $f[a\mapsto b][c\mapsto d]$  with  $a\neq c$  to  $f[a\mapsto b,c\mapsto d]$ . Viewing a tuple with named components as a function mapping names to element values, we also use this notation to specify updates to tuples. We use  $\langle s_1,s_2,\ldots,s_k\rangle$  to denote a sequence of length k, and we write  $\langle a\rangle$  for the empty sequence. We write a>0 to denote a sequence whose first element is a>0 and whose remaining elements form the sequence a>0 the operator ":" associates to the right.

In our semantics, each thread is equipped with a *shadow* copy of global memory. At the start of kernel execution, the shadow memory of all threads is identical. During execution, a thread reads and modifies its shadow memory locally, and maintains a read set and a write set recording those addresses in global memory that the thread has accessed. During each access, the read and write sets are checked for data races. If a race has occurred, execution aborts. When a **barrier** statement is reached with all threads in a group enabled, the write sets are used to build a consistent view of global memory between the threads in a group, the shadow memories are all updated to agree with this view, and the read and write sets are cleared with regard to the accesses of threads within groups.

In what follows, let *P* be a KPL kernel.

3.2.1. Thread, Group, and Kernel States. Let gs denote the number of groups executing P, specified via **groups**: gs in the definition of P. Similarly, let ts denote the number of threads in each group, specified via **threads**: ts. Let  $\mathcal{G}$  denote the set  $\{0, 1, \ldots, gs - 1\}$ , and for each  $i \in \mathcal{G}$ , let  $\mathcal{T}_i$  denote the set  $\{0, 1, \ldots, ts - 1\}$ . Together,  $\mathcal{G}$  and  $\mathcal{T}$  specify the identifiers of all the threads running the kernel, via the function

$$tids(\mathcal{G}, \mathcal{T}) \triangleq \{(i, j) \mid i \in \mathcal{G} \land j \in \mathcal{T}_i\}.$$

We now define thread, group. and kernel states.

Thread States. A thread state is a tuple (l, sh, R, W) where:

- $-l:V \to \text{Word}$  is the local variable store of the thread (recall that V is a set of locations); included are locations gid and lid specifying, respectively, the ID of the group to which the thread belongs, and the ID of the thread within this group.

- $-sh: \mathbb{N} \to \text{Word}$  is the shadow copy of global memory owned by the thread.

- -R,  $W \subseteq \mathbb{N}$  are the read and write sets of the thread recording the global addresses the thread has accessed since the last barrier; these sets are used to detect intragroup data races.

We use  $\tau$  to denote a thread state, and  $\tau.l$ ,  $\tau.sh$ ,  $\tau.R$ ,  $\tau.W$  to refer to the components of  $\tau$ . The set of all thread states is denoted by ThreadStates. Given a local expression e and a thread state  $\tau$ , we write  $e^{\tau}$  for the result of evaluating e according to  $\tau.l$ . We do not

<sup>&</sup>lt;sup>4</sup>Observe that it is not strictly necessary to parameterize  $\mathcal{T}$  in i, as  $\mathcal{T}_i = \{0, 1, \dots, ts-1\}$  for all  $i \in \mathcal{G}$ . However, the parameterization will simplify the presentation of the kernel abstractions presented later in the text.

provide a concrete definition of  $e^{\tau}$ , which depends on the nature of the base type Word and the available operators, except we specify that, for a storage location v,  $v^{\tau} = \tau . l(v)$ .

*Group States.* A *group state* of a group  $i \in \mathcal{G}$  is a tuple  $(\gamma_{ts}, R, W)$  where:

$-\gamma_{ts}: \mathcal{T}_i \to \mathsf{ThreadStates}$  records a thread state for each thread in group i.

-R,  $W \subseteq \mathbb{N} \times \mathcal{T}_i$  are the read and write sets of group i. These are used to detect *intergroup* data races. Each element (x, j) records a global address x accessed by thread j in the group since the start of the kernel. It is necessary to store the local ID j so that when we later reduce executions to just two threads, accesses by threads other than the two selected ones can be identified and removed from R and W.

We use  $\gamma$  (without a subscript) to denote a group state. Given  $\gamma = (\gamma_{ts}, R, W)$ , we use  $\gamma(j)$  to refer to  $\gamma_{ts}(j)$  and we refer to R and R by  $\gamma.R$  and  $\gamma.W$ , respectively. A group state  $\gamma$  of a group i is valid if  $\gamma(j).l(gid) = i$  and  $\gamma(j).l(lid) = j$  for all  $j \in \mathcal{T}_i$ , that is, knowledge of the group id i is consistent across the threads in the group and each thread has a unique local id corresponding to its location in the group.

The set of all valid group states for a group i is denoted GroupStates<sub>i</sub>, and we use GroupStates to denote  $\bigcup_{i \in G}$  GroupStates<sub>i</sub>, the set of all valid group states.

*Kernel States*. A *predicated statement* is a pair (s, p), with  $s \in \mathsf{stmt}$  and  $p \in \mathsf{local\_expr}$ . Intuitively, (s, p) denotes a statement s that should be executed if p holds, and otherwise should have no effect. The set of all predicated statements is denoted PredStmts.

A *kernel state* is a tuple ( $\kappa$ , ss) where:

- $-\kappa: \mathcal{G} \to \text{GroupStates records a group state for each group in the kernel.}$

- $-ss \in \mathsf{PredStmts}^*$  is a sequence of predicated statements to be executed by the kernel.

A kernel state  $(\kappa, ss)$  is valid if, for each  $i \in \mathcal{G}$ ,  $\kappa(i) \in \mathsf{GroupStates}_i$ , that is, each group has a unique id. The set of all valid kernel states is denoted KernelStates.

Observe that a kernel state does not include a single, definitive global memory component: global memory is represented via the shadow copies held by the individual threads in groups, which are initially consistent, and are made consistent again at barriers for threads within a group.

A kernel state  $(\kappa, ss) \in \text{KernelStates}$  is a valid *initial state* of P if:

```

\begin{split} -ss &= \langle (s, true) \rangle, \text{ where } s \text{ is declared in } P \text{ via } \textbf{main} : s. \\ -\kappa(i).R &= \kappa(i).W = \emptyset \text{ for all } i \in \mathcal{G}. \\ -\kappa(i)(j).R &= \kappa(i)(j).W = \emptyset \text{ for all } i \in \mathcal{G} \text{ and } j \in \mathcal{T}_i. \\ -\kappa(i)(j).sh &= \kappa(i')(j').sh \text{ for all } i,i' \in \mathcal{G} \text{ and } j \in \mathcal{T}_i,j' \in \mathcal{T}_{i'}. \\ -\kappa(i)(j).l(v) &= false \text{ for all } i \in \mathcal{G}, \ j \in \mathcal{T}_i \text{ and } v \in V. \end{split}

```

The first requirement ensures that the kernel executes the **main** statement. The second and third requirement guarantee that the read and write sets of both groups and threads are initially empty. The fourth requirement ensures that threads have a consistent but arbitrary initial view of global memory. We single out the final requirement as it impacts on our semantics in a somewhat subtle manner:

Remark 3.1 (Local Storage Locations are Initially false). The fifth requirement ensures that local storage locations are initialized to the value of type Word corresponding to false. Thus, whenever fresh variables are introduced by the semantic rules of Figure 6, these variables initially store the value false. This requirement simplifies our presentation of **break** and **continue** in the rules of Figure 6.

3.2.2. Predicated Execution. We now describe predicated execution of threads, groups, and kernels.

10:14 A. Betts et al.

$$\frac{\neg p^{\tau}}{(\tau,\mathsf{basic\_stmt},p) \to_t \tau} \text{ (T-Disabled)} \qquad \frac{p^{\tau} \quad l' = \tau.l[v \mapsto e^{\tau}]}{(\tau,v := e,p) \to_t \tau[l \mapsto l']} \text{ (T-Assign)}$$

$$\frac{p^{\tau} \quad l' = \tau.l[v \mapsto \tau.sh(e^{\tau})] \quad R' = \tau.R \cup \{e^{\tau}\}}{(\tau,v := sh[e],p) \to_t \tau[l \mapsto l',R \mapsto R']} \text{ (T-Read)}$$

$$\frac{p^{\tau} \quad sh' = \tau.sh[e_1^{\tau} \mapsto e_2^{\tau}] \quad W' = \tau.W \cup \{e_1^{\tau}\}}{(\tau,sh[e_1] := e_2,p) \to_t \tau[sh \mapsto sh',W \mapsto W']} \text{ (T-Write)}$$

Fig. 4. Rules for predicated execution of basic statements by threads.

$$\frac{\forall \ j \in \mathcal{T}_i \ . \ (\gamma(j), \mathsf{basic\_stmt}, p) \to_t \gamma'(j) \qquad \mathsf{group\_race}_i(\gamma')}{(\gamma, \mathsf{basic\_stmt}, p) \to_{g(i)} error} \ (\mathsf{G-RACE})$$

$$\frac{\gamma'.R = \gamma.R \cup \bigcup_{j \in \mathcal{T}_i} . \ (\gamma(j), \mathsf{basic\_stmt}, p) \to_t \gamma'(j) \quad \neg \mathsf{group\_race}_i(\gamma')}{\gamma'.R = \gamma.R \cup \bigcup_{j \in \mathcal{T}_i} (\gamma'(j).R \times \{j\}) \quad \gamma'.W = \gamma.W \cup \bigcup_{j \in \mathcal{T}_i} (\gamma'(j).W \times \{j\})}{(\gamma, \mathsf{basic\_stmt}, p) \to_{g(i)} \gamma'} \ (\text{G-BASIC})$$

(a) Rules for basic statements

$$\frac{\forall \ j \in \mathcal{T}_i \ . \ \neg p^{\gamma(j)}}{(\gamma, \mathbf{barrier}, p) \to_{g(i)} \gamma} \ (\text{G-No-OP}) \qquad \frac{\exists \ j \neq k \in \mathcal{T}_i \ . \ p^{\gamma(j)} \land \neg p^{\gamma(k)}}{(\gamma, \mathbf{barrier}, p) \to_{g(i)} \ error} \ (\text{G-DIVERGENCE})}{\frac{\forall \ j \in \mathcal{T}_i \ . \ p^{\gamma(j)}}{(\gamma, \mathbf{barrier}, p) \to_{g(i)} \ property} \ \forall \ j \in \mathcal{T}_i \ . \ \gamma'(j) = \gamma(j)[sh \mapsto \mathsf{merge}_i(\gamma), R \mapsto \emptyset, W \mapsto \emptyset]}{(\gamma, \mathsf{barrier}, p) \to_{g(i)} \gamma'} \ (\text{G-Sync})$$

(b) Rules for barriers

Fig. 5. Rules for lock-step execution of basic statements and barriers by groups.

Predicated Execution of Threads. The rules of Figure 4 define the binary relation

$$\mathop{\rightarrow}_t \subseteq (\mathsf{ThreadStates} \times \mathsf{PredStmts}) \times \mathsf{ThreadStates}$$

describing the evolution of one thread state to another under execution of a predicated basic statement. For readability, given a thread state  $\tau$  and predicated statement (s, p), we write  $(\tau, s, p)$  instead of  $(\tau, (s, p))$ .

Rule T-Disabled ensures that a predicated statement has no effect if the predicate does not hold, indicated by  $\neg p^{\tau}$  in the premise of the rule; T-Assign updates  $\tau.l$  according to the assignment; T-Read updates the local store of the thread with the appropriate element from the shadow copy of shared memory owned by the thread, and records the address that was read from; rule T-Write is analogous.

Predicated Execution of Groups. Figure 5 defines the binary relation

$$\rightarrow_{g(i)} \subseteq (\mathsf{GroupStates}_i \times \mathsf{PredStmts}) \times (\mathsf{GroupStates}_i \cup \{error\})$$

describing how a group state of a group i mutates into another as a result of executing a predicated basic statement or barrier, where error is a designated error state. As for threads, given a group state  $\gamma$  and predicated statement (s, p), we write  $(\gamma, s, p)$  instead of  $(\gamma, (s, p))$ .

Intragroup data races are detected via rule G-RACE. An intragroup race occurs if there is a thread j in group i such that the write set of j intersects with either the

read or write set of a thread k different from j but in the same group. The predicate  $group\_race_i(\gamma)$  used to detect intragroup races is formally defined as:

group\_race<sub>i</sub>

$$(\gamma) \triangleq \exists j \neq k \in \mathcal{T}_i : \gamma(j).W \cap (\gamma(k).R \cup \gamma(k).W) \neq \emptyset$$

.

Rule G-Race states that if the execution of a basic statement by all threads in a group leads to a group state  $\gamma'$  in which  $\operatorname{group\_race}_i(\gamma')$  holds, then the  $\operatorname{error}$  state is reached.

Lock-step execution of basic statements by a group is achieved by having each thread in the group execute the statement; the order in which they do so is irrelevant due to delayed visibility (G-Basic). The rule requires the execution of the basic statement to be free from intragroup data races. The rule also records which addresses of global memory were read from or written to by the threads in the group; this is achieved by propagating the addresses from the read and write sets of the individual threads into the read and write set of the group.

Execution of **barrier** with all threads in a group disabled has no effect (G-No-Op). If the group is due to execute a **barrier** statement under predicate p but not all threads agree on the truth of p, then the *error* state is reached (G-Divergence). This *precisely* captures the notion of barrier divergence discussed in Section 2.

Rule G-Sync captures the effect of barrier synchronization under predicate p in the case where all threads in the group agree that p is valid. A new group state  $\gamma'$  is constructed, in which for each thread j, the read and write sets of j are empty in  $\gamma'(j)$  and the local component  $\gamma'(j).l$  is identical to the local component for the thread before the barrier. The barrier also enforces a consistent view of shared memory across the group by setting the shadow memories of all threads to the same value. This is achieved by the function  $\text{merge}_i$ . If thread j has recorded a write to a shared memory location z, that is,  $z \in \gamma(j).W$ , then  $\text{merge}_i(\gamma)$  maps z to the value at address z in the shadow memory of thread j, that is, to  $\gamma(j).sh(z)$ .

Formally,  $merge_i(\gamma)$  is a map satisfying the following constraints:

$$\frac{j \in \mathcal{T}_i \quad z \in \gamma(j).W}{\mathsf{merge}_i(\gamma)(z) = \gamma(j).sh(z)} \qquad \qquad \frac{\forall \ j \in \mathcal{T}_i \ . z \notin \gamma.W}{\mathsf{merge}_i(\gamma)(z) = \gamma(0).sh(z)}$$

The value of  $\mathsf{merge}_i(\gamma)$  is guaranteed to be unique, otherwise there exists a z belonging to  $\gamma(j).W$  and  $\gamma(k).W$  for  $j \neq k$ , in which case execution would have aborted earlier via G-Race. Observe that, in the second constraint,  $\gamma(0)$  is arbitrary, and could have been chosen to be any  $\gamma(i)$ ; the value of sh(z) is consistent across threads in this case, since no thread has written to the memory location z.

Predicated Execution of Kernels. Figure 6 defines the binary relation

$$\rightarrow_k \subseteq \mathsf{KernelStates} \times (\mathsf{KernelStates} \cup \{error\})$$

,

where *error* is again a designated error state. This relation describes the evolution of a kernel as it executes a sequence of predicated statements.

Intergroup races are detected via rule K-Inter-Group-Race. An intergroup race occurs if there is a group i such that the write set of i intersects with either the read or write set of a group j different from i (ignoring the particular thread responsible for each read and write). The predicate kernel\_race( $\kappa$ ) used to detect intergroup races is formally defined as:

$$kernel\_race(\kappa) \triangleq \exists i \neq j \in \mathcal{G} . fst(\kappa(i).W) \cap fst(\kappa(j).R \cup \kappa(j).W) \neq \emptyset,$$

where  $fst(X) = \{x \mid (x,y) \in X\}$ . Rule K-Inter-Group-Race states that if collective execution of a predicated basic statement by all groups leads to a state  $\kappa'$  in which kernel\_race( $\kappa'$ ) holds, then the *error* state is reached. Rule K-Intra-Group-Race detects intragroup races by lifting the application of rule G-Race to the kernel level.

10:16 A. Betts et al.

$$\frac{\forall i \in \mathcal{G} . (\kappa(i), \mathsf{basic\_stmt}, p) \to_{g(i)} \kappa'(i) \qquad \mathsf{kernel\_race}(\kappa')}{(\kappa, (\mathsf{basic\_stmt}, p) : ss) \to_k error} \quad (\mathsf{K-INTRA-GROUP-RACE})$$

$$\frac{\exists \ i \in \mathcal{G} . (\kappa(i), \mathsf{basic\_stmt}, p) \to_{g(i)} error}{(\kappa, (\mathsf{basic\_stmt}, p) \mapsto_{g(i)} \kappa'(i) \qquad \neg \mathsf{kernel\_race}(\kappa')} \quad (\mathsf{K-BASIC})$$

$$\frac{\forall \ i \in \mathcal{G} . (\kappa(i), \mathsf{basic\_stmt}, p) \to_{g(i)} \kappa'(i) \qquad \neg \mathsf{kernel\_race}(\kappa')}{(\kappa, (\mathsf{basic\_stmt}, p) : ss) \to_k (\kappa', ss)} \quad (\mathsf{K-BASIC})$$

$$(a) \ \mathsf{Rules} \ \mathsf{for} \ \mathsf{basic} \ \mathsf{statements}$$

$$\frac{\exists \ i \in \mathcal{G} . (\kappa(i), \mathsf{barrier}, p) \to_{g(i)} error}{(\kappa, (\mathsf{barrier}, p) : ss) \to_k error} \quad (\mathsf{K-DIVERGENCE})$$

$$\frac{\forall \ i \in \mathcal{G} . (\kappa(i), \mathsf{barrier}, p) \to_{g(i)} \kappa'(i)}{(\kappa, (\mathsf{barrier}, p) : ss) \to_k (\kappa', ss)} \quad (\mathsf{K-SYNC})$$

$$\frac{\forall \ i \in \mathcal{G} . (\kappa(i), \mathsf{barrier}, p) \to_{g(i)} \kappa'(i)}{(\kappa, (\mathsf{barrier}, p) : ss) \to_k (\kappa', ss)} \quad (\mathsf{K-SYNC})$$

$$\frac{\forall \ i \in \mathcal{G} . (\kappa(i), \mathsf{barrier}, p) \to_{g(i)} \kappa'(i)}{(\kappa, (\mathsf{barrier}, p) : ss) \to_k (\kappa, (S_1, p) : (S_2, p) : ss)} \quad (\mathsf{K-SEQ})$$

$$\frac{\mathsf{fresh} \ v \in V}{(\kappa, (\mathsf{coal} \ x \ S, p) : ss) \to_k (\kappa, (S_1, p) : (S_2, p) : ss)} \quad (\mathsf{K-VAR})$$

$$\frac{\mathsf{fresh} \ v \in V}{(\kappa, (\mathsf{inf} \ e \ S_1 \ else \ S_2, p) : ss) \to_k (\kappa, (\mathsf{inf} \ e \ else \ S_2, p) : ss)} \to_k (\kappa, (\mathsf{inf} \ else \ S, p) : ss)} \quad (\mathsf{K-OPEN})$$

$$\frac{\exists \ i \in \mathcal{G} . \ j \in \mathcal{T}_i . (p \land e)^{\kappa(i)(j)} \quad \mathsf{fresh} \ u, v \in V}{(\kappa, (\mathsf{while} \ e \ S, p) : ss) \to_k (\kappa, (\mathsf{inf} \ else \ S, p) : ss)} \quad (\mathsf{K-ITER})$$

$$\frac{\forall \ i \in \mathcal{G} . \ j \in \mathcal{T}_i . \neg (p \land e)^{\kappa(i)(j)} \quad \mathsf{fresh} \ u, v \in V}{(\kappa, (\mathsf{while} \ e \ S, p) : ss) \to_k (\kappa, (\mathsf{inf} \ else \ S, p) : ss)} \rightarrow_k (\mathsf{K-Call})$$

$$\frac{\forall \ i \in \mathcal{G} . \ j \in \mathcal{T}_i . \neg (p \land e)^{\kappa(i)(j)} \quad \mathsf{fresh} \ u, v \in V}{(\kappa, (\mathsf{while} \ e \ S, p) : ss) \to_k (\kappa, (\mathsf{inf} \ else \ S, p) : ss)} \rightarrow_k (\mathsf{K-Call})$$

$$\frac{\forall \ i \in \mathcal{G} . \ j \in \mathcal{T}_i . \neg (p \land e)^{\kappa(i)(j)} \quad \mathsf{fresh} \ u, v \in V}{(\kappa, (\mathsf{while} \ else \ S, p) : ss) \to_k (\kappa, (\mathsf{inf} \ else \ S, p) : ss)} \to_k (\mathsf{inf} \ else \ S, p) : ss) \to_k (\mathsf{inf} \ else \ S, p) : ss)} \to_k (\mathsf{inf} \ else \ S, p) : ss) \to_k (\mathsf{inf} \ else \ S, p) : ss) \to_k (\mathsf{inf} \ else \ S, p) : ss)} \to_k (\mathsf{inf} \ else \ S, p) : ss) \to_k$$

Fig. 6. Rules for lock-step execution of statements by kernels.

Collective execution of a predicated basic statement is achieved by having every group execute the statement; the order in which they do so is irrelevant (K-Basic). The rule requires that the collective execution was free from intergroup data races (via the  $\neg$ kernel\_race( $\kappa'$ ) condition) and intragroup data races (via the condition that each group state in  $\kappa$  transitions to a non-error group state in  $\kappa'$ ).

Rule K-Divergence lifts application of rule G-Divergence to the kernel level, that is, the kernel transitions to the *error* state if barrier divergence is detected in one of the groups. Collective execution of a **barrier** statement in the absence of barrier

divergence is achieved via rule K-Sync where each group transitions to a new group state either by rule G-Sync or rule G-No-Op. Observe that the read and write sets of groups are not cleared because barriers are used solely for intragroup synchronization and do not achieve intergroup synchronization.

The remaining rules of Figure 6 describe predicated execution of compound statements. Rule K-Seq is straightforward. Rule K-Var creates storage for a new local variable x by allocating a fresh location v in V and substituting all occurrences of x in S by v; we use  $S[x \mapsto v]$  to denote this substitution. Rule K-IF decomposes a conditional statement into a sequence of predicated statements: the guard of the conditional is evaluated into a new location v; the then branch  $S_1$ , is executed by all threads in all groups under predicate  $p \wedge v$  (where p is the predicate already in place on entry to the conditional), and the else branch  $S_2$ , is executed by all threads in all groups under predicate  $p \wedge \neg v$ .

Rules K-Open, K-Iter, and K-Done together model predicated execution of a **while** loop. In what follows, we say that a **break** or **continue** statement is *top-level* in a loop if the statement appears in the loop body but is not nested inside any further loops.

Rule K-Open converts a **while** loop into a **while** loop by creating fresh storage to model **break** statements. A fresh location v is selected; v records whether a thread has executed a **break** statement associated with the **while** loop. Like all local storage, v initially has the value false (see Remark 3.1): no thread has executed **break** on loop entry. The function belim is applied to the loop body. This function takes a statement S and a location v and replaces each top-level **break** statement inside S by the statement v := true. The predicate for the execution of the **while** loop becomes  $p \land \neg v$  to model that the statements in the loop have no effect after the execution of a **break** statement. A similar technique to model **break** statements is used by Habermaier and Knapp [2012].

The K-ITER rule models execution of loop iterations and handles **continue** statements. The rule fires each time a loop iteration is executed. For a given loop iteration, two fresh local storage locations u and v are selected and (as per Remark 3.1) both are initialized to false. Location u is used to store the valuation of the loop guard. Location v is used to record whether a thread has executed a top-level **continue** statement during the current loop iteration. The value of v is initially false, since no thread has executed a continue statement at the beginning of an iteration. The statement u := e (executed under the enclosing predicate p) evaluates the loop guard into u. The function celim is applied to the loop body; this function takes a statement S and a location v and replaces each top-level **continue** statement inside S by the statement v := true. The loop body, after elimination of **continue** statements, is executed under the predicate  $p \wedge u \wedge \neg v$ : a thread is enabled during the current iteration if the incoming predicate holds (p), the loop guard evaluates to true at the start of the iteration (u) and the thread has not executed a **continue** statement  $(\neg v)$ . Note that, due to rule K-Open, the incoming predicate p includes a conjunct recording whether the thread has executed a **break** statement. After the loop body, the **while** construct is considered again.

Thus, all threads continuously execute the loop body using K-ITER until, for *every* thread in *every* group, (a) the enclosing predicate *p* becomes *false*, either because this predicate was *false* on loop entry or because the thread has executed **break**, or (b) the loop condition no longer holds for the thread.<sup>6</sup> When (a) or (b) holds for all threads, loop exit is handled by rule K-Done.

<sup>&</sup>lt;sup>5</sup>Note that u and v are not reused between loop iterations: a fresh u and v are selected at the start of each loop iteration. Hence, there is no need to reset u and v at the end of a loop iteration.

<sup>&</sup>lt;sup>6</sup>Execution of **continue** does not directly contribute to the conditions under which threads exit a loop. This is because on executing a **continue** statement a thread becomes disabled for the remainder of the current

10:18 A. Betts et al.

The rule K-Call models the execution of a call to a procedure f. This involves executing the statement corresponding to the body of the called procedure (Body(f)) after replacing all occurrences of its formal parameter (Param(f)) with a location storing the evaluation result of the actual parameter expression. All threads execute the entire body of a procedure in lock-step. A fresh storage location v is used to record whether a thread has executed a return statement. Initially, this location is set to false, and the function relim replaces each return statement in Body(f) with the statement v := true. The procedure body is executed under the predicate  $p \land \neg v$  (where p is the existing predicate of execution at the point of the call) so that execution of a return statement by a thread is simulated by the thread becoming disabled for the remainder of the procedure body.

#### 3.3. Formalization in Isabelle

The definitions in this section have been formalized in the Isabelle proof assistant [Nipkow et al. 2002] and are available from the Archive of Formal Proofs [Wickerson 2014]. For the most part, the Isabelle definitions closely resemble those presented earlier, but there are three notable differences. First, we do not model the abuse of notation whereby  $\gamma(j)$  abbreviates  $\gamma_{ts}(j)$ , since the use of such type coercions was found to necessitate many additional type annotations. Second, we extend kernel states with a third component, to record all the variables that have been used. This is necessary for calculating the fresh variables required by several of the rules in Figure 6, but is left implicit, in accordance with common practice, in the previous subsections. Third, because Isabelle does not allow dependent types, we cannot define functions between arbitrary sets (at least not without extensive use of typedefs, which can complicate proofs) such as  $\gamma_{ts}: \mathcal{T}_i \to \text{ThreadStates}$ . In such situations, we instead declare  $\gamma_{ts}$  as a partial function from local IDs to ThreadStates and make  $dom(\gamma_{ts}) = \mathcal{T}_i$  available as an assumption when proving theorems.

In Section 4.2, we discuss our experience using these formalized definitions to partially mechanize a proof of soundness for the *two-thread reduction*; this reduction is our next main contribution.

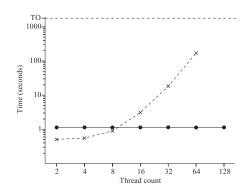

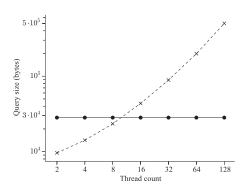

# 4. THE TWO-THREAD REDUCTION

The SDV operational semantics of Section 3 has all threads execute in lock-step. As such, our massively parallel N-threaded kernel can be encoded as a single sequential program, where each instruction is replicated N times, and where assertions are inserted to check for data races and barrier divergence. In principle, existing techniques for sequential program verification can be applied directly to this program and, as discussed in detail in Section 5, we have investigated the use of the Boogie verification system [Barnett et al. 2005] for this purpose. We have found that directly encoding massively parallel kernels as sequential programs leads to infeasibly large verification conditions if an explicit representation of threads is used. In Section 6.4, we illustrate this blow-up in verification condition size, and the corresponding effect this has on verification performance, using a simple example. The explicit representation can be replaced with quantification over all threads, but we have found this to lead to verification conditions that cannot be automatically handled by Z3, a state-of-the-art theorem prover [de Moura and Bjørner 2008], which Boogie uses by default.<sup>7</sup>

loop iteration, but the thread is *re-enabled* at the start of the next iteration, provided the loop guard still holds for the thread.

<sup>&</sup>lt;sup>7</sup>The difficulty of reasoning about quantifiers is, of course, not specific to Z3, but a general obstacle faced by any automated theorem prover.

To overcome these practical limitations and achieve scalable reasoning, we describe an alternative encoding that involves reducing the number of threads under consideration from N to just two.

Observe that the properties of data race- and barrier divergence-freedom are *pairwise* properties: a race occurs when accesses by two threads conflict, and barrier divergence occurs when a barrier is executed in a state where one thread is enabled and another thread in the same group is disabled. Therefore, we can consider an operational semantics where the predicated execution of only *two* threads is modeled. If we can use such a semantics to prove a kernel data race- and barrier divergence-free for a pair of distinct but otherwise *arbitrary* threads, we can conclude correctness of the kernel. This is because the verification process considers all possible execution traces so that, because the two threads under consideration are arbitrary, interactions between all possible pairs of threads are implicitly considered.

Formally, if the original execution involves all of the threads in  $tids(\mathcal{G}, \mathcal{T})$  (see Section 3.2.1), then we need to check data race- and barrier divergence-freedom for all restrictions of  $(\mathcal{G}, \mathcal{T})$  to a pair of threads, that is, for restrictions to  $(\mathcal{G}', \mathcal{T}')$  such that

```

-\mathcal{G}' \subseteq \mathcal{G} and \mathcal{T}'_i \subseteq \mathcal{T}_i for all i \in \mathcal{G}', and -tids(\mathcal{G}', \mathcal{T}') consists of exactly two elements.

```

It is important to clarify that in practice we do not enumerating all possible twothread reductions. Rather, as discussed in Section 5, when we discuss the implementation of GPUVerify, we use symbolic constants to model the identifiers of two arbitrary threads during analysis.

We now present the reduction to a pair of threads formally and prove that it is sound. Our GPUVerify verification technique and tool, described in Section 5, depend on this reduction. The design of the PUG verifier for CUDA kernels by Li and Gopalakrishnan [2010] also hinges on a reduction to a pair of threads. However, this is the first formal presentation and proof of soundness for the reduction method.

Observe that the definitions of (valid) group and kernel states carry over to the sets  $\mathcal{G}'$  and  $\mathcal{T}'_i$  as defined earlier and that the same holds for the kernel-level execution rules from Figure 6. However, for the aforementioned approach to be sound, we must *approximate* shared state handling, abstracting the values written to the shared state by threads that are not modeled. This can be achieved in multiple ways. We consider the following strategies:

*Equality abstraction:* Threads manipulate a shadow copy of the shared state. At a barrier, the shadow copies are set to be *arbitrary*, but *equal*. Thus, on leaving the barrier, the threads have a consistent view of shared memory.

Adversarial abstraction: The shared state is made irrelevant; reads from the shared state into local variables are replaced with nondeterministic assignments to local variables.

We have found several example kernels where race-freedom hinges on threads agreeing on the values read from certain shared locations. In these cases, the adversarial abstraction is too coarse for successful verification. However, in many cases, it does not matter what specific value is stored in shared memory, only that all threads see the same value. The equality abstraction suffices for such cases. Our use of equality abstraction allows us to improve upon the precision of the work of Li and Gopalakrishnan [2010], which is limited to the adversarial abstraction.

The execution relation for equality abstraction, written  $\rightarrow_{k,\mathcal{E}(\mathcal{G}',\mathcal{T}')}$ , is obtained by replacing rule G-Sync in Figure 5 with rule G-Sync-Eq from Figure 7(a), and replacing all references to  $\mathcal{G}$  and  $\mathcal{T}$  in all other semantic rules in Figures 5 and 6 with  $\mathcal{G}'$  and  $\mathcal{T}'$ ,

10:20 A. Betts et al.

$$\frac{\forall \ j \in \mathcal{T}_i' \ . \ p^{\gamma(j)}}{(\gamma, \mathbf{barrier}, p) \rightarrow_{\sigma(i)} \gamma'} \frac{\exists sh' \ . \ \forall \ j \in \mathcal{T}_i' \ . \ \gamma'(j) = \gamma(j)[sh \mapsto sh', R \mapsto \emptyset, W \mapsto \emptyset]}{(\gamma, \mathbf{barrier}, p) \rightarrow_{\sigma(i)} \gamma'}$$

(G-Sync-Eq)

(a) Updated rule for the equality abstraction

$$\frac{p^{\tau} \quad \exists \ v' \ . \ l' = \tau.l[v \mapsto v'] \qquad R' = \tau.R \cup \{e^{\tau}\}}{(\tau, v := sh[e], p) \rightarrow_t \tau[l \mapsto l', R \mapsto R']} \text{ (T-Read-Adv)}$$

$$\frac{p^{\tau} \quad W' = \tau.W \cup \{e_1^{\tau}\}}{(\tau, sh[e_1] := e_2, p) \rightarrow_t \tau[sh \mapsto sh', W \mapsto W']} \text{ (T-Write-Adv)}$$

$$\frac{\forall \ j \in \mathcal{T}_i' \ . \ p^{\gamma(j)} \qquad \forall \ j \in \mathcal{T}_i' \ . \ \exists \ sh' \ . \ \gamma'(j) = \gamma(j)[sh \mapsto sh', R \mapsto \emptyset, W \mapsto \emptyset]}{(\gamma, \mathbf{barrier}, p) \rightarrow_{g(j)} \gamma'} \text{ (G-Sync-Adv)}$$

(b) Updated rules for the adversarial abstraction

Fig. 7. Rules for the adversarial and equality abstractions.

respectively. In rule G-Sync-Eq, instead of merging the shared states of the threads in group i, an arbitrary value is chosen for the shared state and the shadow copy of each thread in the group is assigned this value. Clearing of read and write sets and checking for barrier divergence is left unchanged.

The execution relation for adversarial abstraction, written  $\rightarrow_{k,\mathcal{A}(\mathcal{G}',\mathcal{T}')}$ , is obtained by replacing rules T-Read and T-Write in Figure 4, and G-Sync in Figure 5, with the rules T-Read-Adv, T-Write-Adv, and G-Sync-Adv from Figure 7(b), respectively, as well as replacing all references to  $\mathcal{G}$  and  $\mathcal{T}$  in all other semantic rules in Figures 5 and 6 with  $\mathcal{G}'$  and  $\mathcal{T}'$ , respectively. Rule T-Read-Adv makes the shared state irrelevant by updating the local store with an arbitrary value v' rather than one obtained from the shared state, although it still logs the read in the read set of the thread. Rule T-Write-Adv sets the shared state to an arbitrary value sh' but still logs the write in the write set of the thread. Similar to G-Sync-Eq, rule G-Sync-Adv does away with merging the shared states of the threads in a group i; the rule sets the shared state of each thread to an arbitrary value, clears the read and write sets and checks for barrier divergence.

Comparing rules G-Sync-Eq and G-Sync-Adv, the premises are almost identical. The key difference is that in rule G-Sync-Eq a single value is selected for the shared state, common to all threads, while in rule G-Sync-Adv a value for the shared state is selected separately for each thread. Thus, with the adversarial abstraction, threads do not see a unified view of shared memory after a barrier synchronization.

#### 4.1. Soundness of the Two-Thread Reduction

We first prove the soundness of the two-thread reduction when using the equality abstraction.

Throughout, let a concrete execution be a nonempty sequence of kernel states

$$\langle (\kappa_0, ss_0), \ldots, (\kappa_{n-1}, ss_{n-1}) \rangle$$

where  $(\kappa_0, ss_0)$  is a valid initial kernel state and where each successive pair is related by the  $\rightarrow_k$  relation of Figure 6. An *execution under the equality abstraction with respect to*

<sup>&</sup>lt;sup>8</sup>Technically, this rule does not need to change the shared state at all because the shared state is ignored by the T-Read-Adv. However, the rule in its current form is better able to simulate the concrete T-Write rule in the upcoming soundness proof.

$(\mathcal{G}', \mathcal{T}')$  is defined similarly, except that it uses the  $\rightarrow_{k,\mathcal{E}(\mathcal{G}',\mathcal{T}')}$  relation instead. Recalling that  $\mathcal{G} = \{0, 1, \dots, gs-1\}$  and that  $\mathcal{T}_i = \{0, 1, \dots, ts-1\}$  for each  $i \in \mathcal{G}$ , we now have the following:

Theorem 4.1 (Soundness: Equality Abstraction). Let P be a KPL kernel executed by gs groups and ts threads per group. If no execution of P under the equality abstraction with respect to any  $(\mathcal{G}', \mathcal{T}')$  (representing a pair of threads) leads to error, then no concrete execution of P leads to error.

PROOF. We prove the contrapositive. Thus, let us assume that P has a concrete execution leading to error. We will show that there also exists an execution for P under the equality abstraction that leads to error.

Let the concrete execution of *P* that leads to *error* be:

$$\rho \triangleq \langle (\kappa_0, ss_0), \dots, (\kappa_{n-1}, ss_{n-1}) \rangle.$$

We now construct an execution of P under the equality abstraction with respect to some  $(\mathcal{G}', \mathcal{T}')$  (representing a pair of threads) that also leads to *error*.

Observe that in the final state  $(\kappa_{n-1}, ss_{n-1})$ , either rule K-Inter-Group-Race, K-Inter-Group-Race, or K-Divergence applies because only these rules can lead to error. In each case, exactly two threads are responsible for the rule being applicable. Assume that these threads are  $s=(i_1,j_1)$  and  $t=(i_2,j_2)$ , with the first component of each pair being the group ID of the thread and the second component being the local ID. Define  $\mathcal{G}'$  and  $\mathcal{T}'$  as follows:

$$- ext{if } i_1 = i_2, ext{ then } \mathcal{G}' = \{i_1\} ext{ and } \mathcal{T}_{i_1} = \{j_1, j_2\}; ext{ and } \\ - ext{if } i_1 \neq i_2, ext{ then } \mathcal{G}' = \{i_1, i_2\}, \mathcal{T}_{i_1} = \{j_1\} ext{ and } \mathcal{T}_{i_2} = \{j_2\}.$$

We now define a function  $proj^{s,t}$  that takes a kernel state and filters out all components not pertaining to s and t:

$$proj^{s,t}(\kappa, ss) \triangleq (\kappa', ss),$$

where  $dom(\kappa') = \mathcal{G}'$  and  $\kappa'(i) = proj_i^{s,t}(\kappa(i))$  for all  $i \in \mathcal{G}'$ . For group states, we define:

$$proj_{i}^{s,t}(\gamma_{ts}, R, W) \triangleq (\gamma_{ts}|_{\mathcal{T}'_{i}}, R \cap (\mathbb{N} \times \mathcal{T}'_{i}), W \cap (\mathbb{N} \times \mathcal{T}'_{i})),$$

where  $f \upharpoonright_A$  denotes the restriction of the domain of f to A. The intersection with  $\mathbb{N} \times \mathcal{T}'_i$  restricts the read and write sets of the group to only those accesses by the thread(s) in  $\mathcal{T}'_i$ .