# **Advanced Computer Architecture Chapter 7:**

### **Multi-threading**

November 2023 Paul H J Kelly

These lecture notes are partly based on the course text, Hennessy and Patterson's Computer Architecture, a quantitative approach (3<sup>rd</sup> and 4<sup>th</sup> eds), and on the lecture slides of David Patterson and John Kubiatowicz's Berkeley course

#

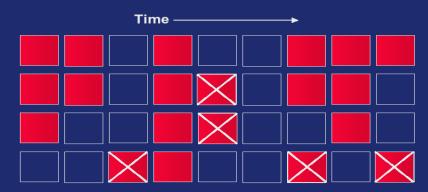

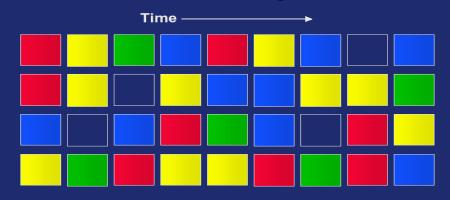

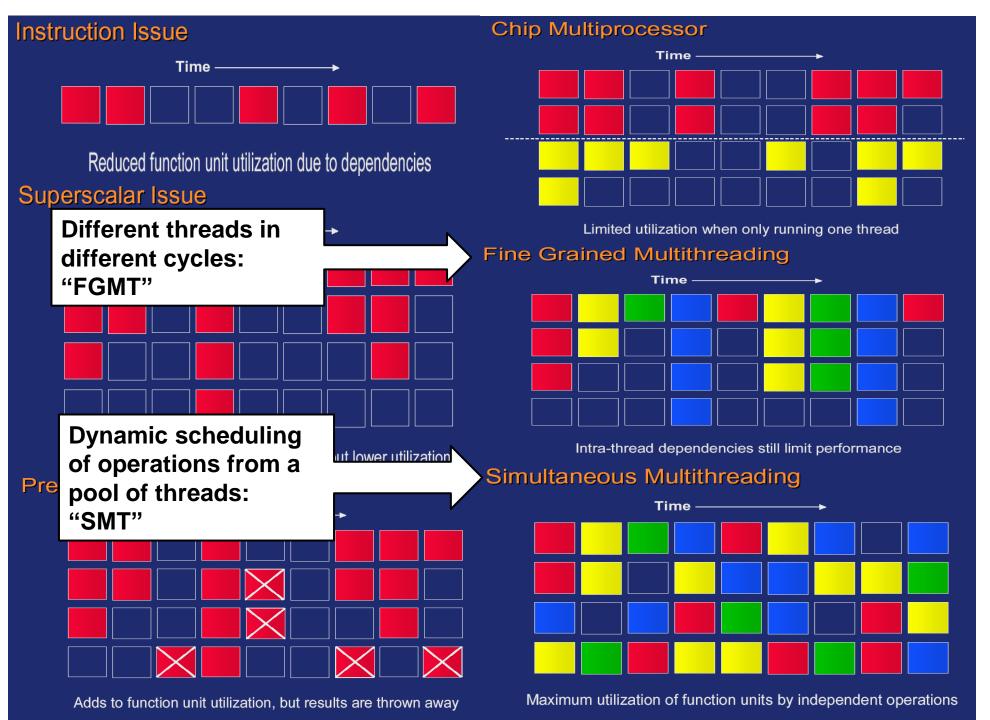

Reduced function unit utilization due to dependencies

#### Superscalar Issue

Instruction Issue

Superscalar leads to more performance, but lower utilization

#### **Predicated Issue**

Adds to function unit utilization, but results are thrown away

Limited utilization when only running one thread

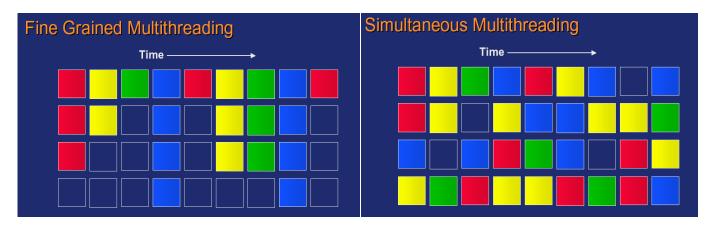

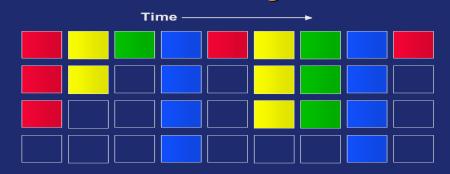

#### Fine Grained Multithreading

Intra-thread dependencies still limit performance

#### Simultaneous Multithreading

Maximum utilization of function units by independent operations

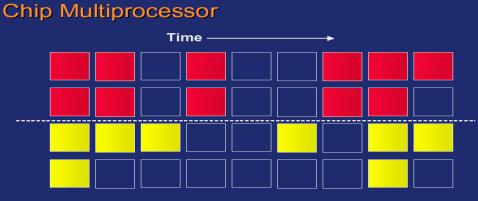

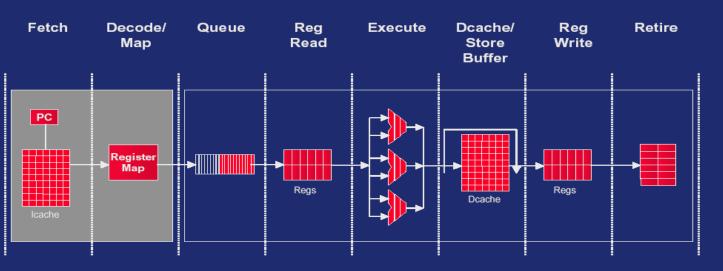

#### Basic Out-of-order Pipeline

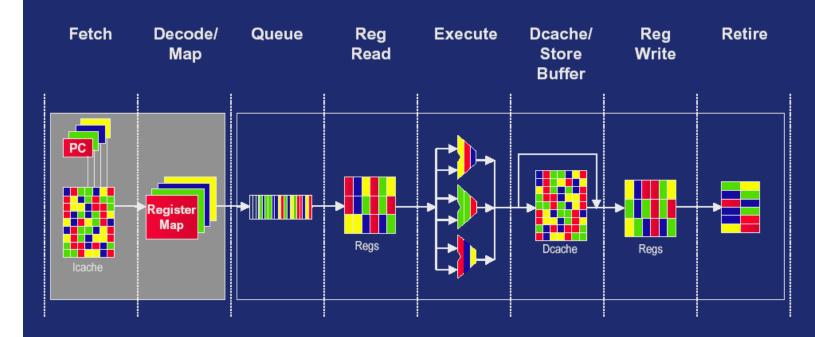

### **SMT Pipeline**

- Mar. Alpha 21464

- One CPU with 4 Thread Processing Units (TPUs)

- "6% area overhead over single-thread 4-issue CPU"

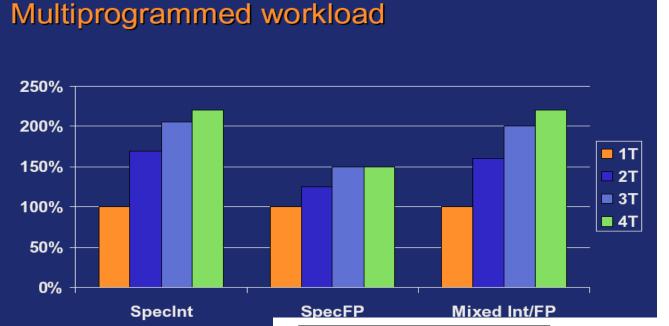

# SMT performance

Alpha 21464

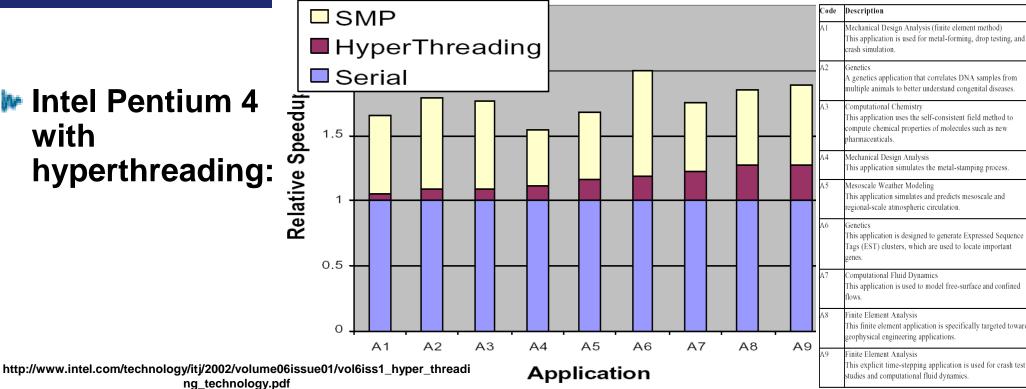

Intel Pentium 4 with hyperthreading:

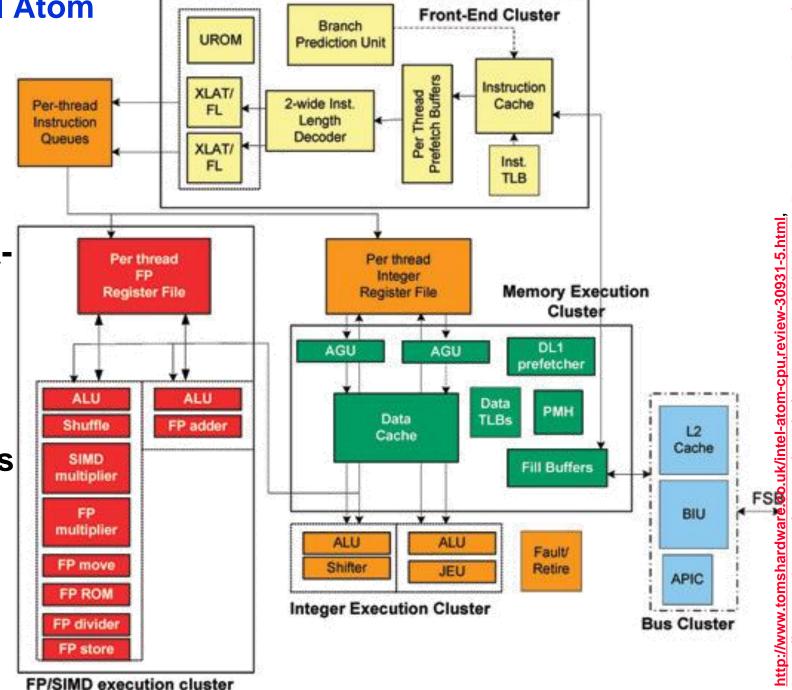

SMT in the Intel Atom (Silverthorne)

Intel's bid to steal back some of the low-power market for IA-32 and Windows

- **In-order**

- 2-way SMT

- 2 instructions per cycle

(from same or different threads)

#### Each thread runs slow?

# **SMT** issues

➡ The point of Simultaneous Multithreading is that resources are dynamically assigned, so if only one thread can run it can run faster

#### SMT threads contend for resources

- Possibly symbiotically?

- One thread is memory-intensive, one arithmetic-intensive?

- Possibly destructively

- thrashing the cache? Other shared resources.... (TLB?)

- Which resources should be partitioned per-thread, and which should be shared on-demand?

- SMT threads need to be scheduled fairly

- Can one thread monopolise the whole CPU?

- Denial of service risk

- Slow thread that suffers lots of cache misses fills RUU and blocks issue

#### Side channels:

one thread may be able observe another's traffic and deduce what it's doing

# SMT - latency-hiding

- SMT threads exploit memory-system parallelism

- Easy way to get lots of memory accesses in-flight

- "Latency hiding" overlapping data access with compute

- What limits the number of threads we can have?

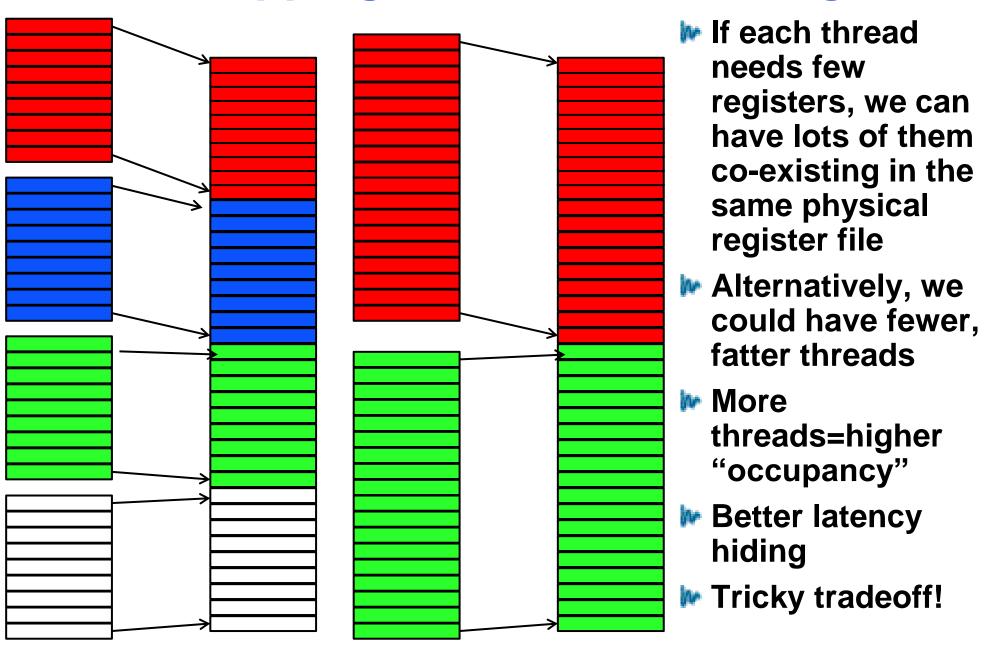

- SMT threads need a *lot* of registers

- **▶** A lot of logical registers but they share physical registers?

### In a machine without register renaming

- What about statically partitioning the register file based on the number of registers each thread actually needs?

- This is what many GPUs do

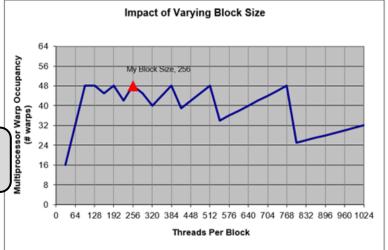

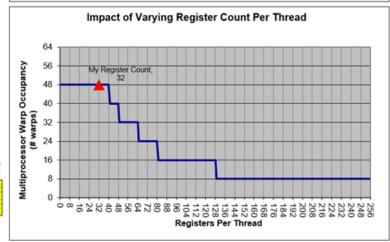

- ▶ Leads to tradeoff: lots of lightweight threads to maximise latency hiding? Or fewer heavyweight threads that benefit from lots of registers?

- Nvidia and AMD call this "occupancy"

# Mapping threads into the register file

#### **CUDA Occupancy Calculator** Click Here for detailed instructions on how to use this occupancy calculator. For more information on NVIDIA CUDA, visit http://developer.nvidia.com/cuda Just follow steps 1, 2, and 3 below! (or click here for help) Your chosen resource usage is indicated by the red triangle on the graphs. The other data points represent the range of possible block sizes, register counts, and shared memory 1.) Select Compute Capability (click): 8.6 (Help) allocation. 1.b) Select Shared Memory Size Config (bytes) 65536 Impact of Varying Block Size 1.c) Select CUDA version 11.1 2.) Enter your resource usage: Multiprocessor Warp Occupancy Threads Per Block 256 56 Registers Per Thread 128 User Shared Memory Per Block (bytes) 2048 48 40 (Don't edit anything below this line) 32 3.) GPU Occupancy Data is displayed here and in the graphs: #registers 512 **Active Threads per Multiprocessor** My Block Size, 256 16 Active Warps per Multiprocessor 16 per thread Active Thread Blocks per Multiprocessor 33% Occupancy of each Multiprocessor 64 128 192 256 320 384 448 512 576 640 704 768 832 896 960 1024 Physical Limits for GPU Compute Capability: 8.6 32 Threads per Warp Threads Per Block Max Warps per Multiprocessor 48 Max Thread Blocks per Multiprocessor 16 Impact of Varying Register Count Per Thread 1536 Max Threads per Multiprocessor Maximum Thread Block Size 1024 Registers per Multiprocessor 65536 64 Max Registers per Thread Block 65536 56 Max Registers per Thread 255 Occupancy Shared Memory per Multiprocessor (bytes) 65536 48 Max Shared Memory per Block 65536 Register allocation unit size 256 Register allocation granularity warp sor Warp 32 Shared Memory allocation unit size 128 Warp allocation granularity My Register Count Shared Memory Per Block (bytes) (CUDA runtime use) 1024 = Allocatable Allocated Resources Per Block Limit Per SM Blocks Per SM Warps (Threads Per Block / Threads Per Warp) 16 8 (Warp limit per SM due to per-warp reg count) 085235588 Shared Memory (Bytes) 2048 65536 Note: SM is an abbreviation for (Streaming) Multiprocessor Registers Per Thread Blocks/SM \* Warps/Block = Warps/SM Maximum Thread Blocks Per Multiprocessor Limited by Max Warps or Max Blocks per Multiprocessor Limited by Registers per Multiprocessor imited by Shared Memory per Multiprocessor Physical Max Warps/SM = 48 Note: Occupancy limiter is shown in orange Occupancy = 16 / 48 = 33% **CUDA Occupancy Calculator** 11.1 Version: Copyright and License

#### **CUDA Occupancy Calculator** Click Here for detailed instructions on how to use this occupancy calculator. For more information on NVIDIA CUDA, visit http://developer.nvidia.com/cuda Just follow steps 1, 2, and 3 below! (or click here for help) Your chosen resource usage is indicated by the red triangle on the graphs. The other data points represent the range of possible block sizes, register counts, and shared memory allocation. 1.) Select Compute Capability (click): 8.6 (Help) 1.b) Select Shared Memory Size Config (bytes) 65536 Impact of Varying Block Size 1.c) Select CUDA version 11.1 2.) Enter your resource usage: Occupancy Threads Per Block 256 (Help) 56 Registers Per Thread 64 48 2048 User Shared Memory Per Block (bytes) (Don't edit anything below this line) 3.) GPU Occupancy Data is displayed here and in the graphs: 1024 #registers Active Threads per Multiprocessor Active Warps per Multiprocessor 32 16 per thread Active Thread Blocks per Multiprocessor Occupancy of each Multiprocessor 67% 64 128 192 256 320 384 448 512 576 640 704 768 832 896 960 1024 Physical Limits for GPU Compute Capability: 8.6 Threads Per Block Threads per Warp 32 48 Max Warps per Multiprocessor Max Thread Blocks per Multiprocessor 16 Impact of Varying Register Count Per Thread Max Threads per Multiprocessor 1536 Maximum Thread Block Size 1024 Registers per Multiprocessor 65536 Max Registers per Thread Block 65536 Max Registers per Thread 255 56 Occupancy Shared Memory per Multiprocessor (bytes) 65536 65536 Max Shared Memory per Block Register allocation unit size 256 My Register Count Register allocation granularity warp Multiprocessor Warp 32 Shared Memory allocation unit size 128 Warp allocation granularity Shared Memory Per Block (bytes) (CUDA runtime use) 1024 = Allocatable Limit Per SM Blocks Per SM Allocated Resources Per Block (Threads Per Block / Threads Per Warp) Warps 8 48 32 Registers (Warp limit per SM due to per-warp reg count) 8 Shared Memory (Bytes) 2048 65536 Note: SM is an abbreviation for (Streaming) Multiprocessor Registers Per Thread Maximum Thread Blocks Per Multiprocessor Blocks/SM \* Warps/Block = Warps/SM imited by Max Warps or Max Blocks per Multiprocessor 32 Limited by Registers per Multiprocessor imited by Shared Memory per Multiprocessor Note: Occupancy limiter is shown in orange Physical Max Warps/SM = 48 Occupancy = 32 / 48 = 67% CUDA Occupancy Calculator Version: 11.1 Copyright and License

# **CUDA Occupancy Calculator**

Just follow steps 1, 2, and 3 below! (or click here for help)

1.) Select Compute Capability (click): 8.6 1.b) Select Shared Memory Size Config (bytes) 65536 1.c) Select CUDA version 11.1

2.) Enter your resource usage: Registers Per Thread

(Don't edit anything below this line)

Threads Per Block

User Shared Memory Per Block (bytes)

3.) GPU Occupancy Data is displayed here and in the graphs: Active Threads per Multiprocessor

1536 Active Warps per Multiprocessor Active Thread Blocks per Multiprocessor Occupancy of each Multiprocessor 100%

Physical Limits for GPU Compute Capability: 8.6 Threads per Warp

32 Max Warps per Multiprocessor 48 Max Thread Blocks per Multiprocessor 16 Max Threads per Multiprocessor 1536 Maximum Thread Block Size 1024 Registers per Multiprocessor 65536 Max Registers per Thread Block 65536

Max Registers per Thread 255 Shared Memory per Multiprocessor (bytes) 65536 Max Shared Memory per Block 65536 Register allocation unit size 256 Register allocation granularity warp

Shared Memory allocation unit size 128 Warp allocation granularity Shared Memory Per Block (bytes) (CUDA runtime use) 1024

= Allocatable Per Block Limit Per SM Blocks Per SM Allocated Resources (Threads Per Block / Threads Per Warp) 8 8 64 Registers (Warp limit per SM due to per-warp reg count) 2048 65536 32 Shared Memory (Bytes)

Note: SM is an abbreviation for (Streaming) Multiprocessor

Maximum Thread Blocks Per Multiprocessor Blocks/SM \* Warps/Block = Warps/SM

Limited by Max Warps or Max Blocks per Multiprocessor 8 imited by Registers per Multiprocessor. imited by Shared Memory per Multiprocessor

Note: Occupancy limiter is shown in orange

Physical Max Warps/SM = 48 Occupancy = 48 / 48 = 100%

(Help)

(Help)

#registers

per thread

2048

**CUDA Occupancy Calculator** 11.1 Copyright and License

Click Here for detailed instructions on how to use this occupancy calculator. For more information on NVIDIA CUDA, visit http://developer.nvidia.com/cuda

Your chosen resource usage is indicated by the red triangle on the graphs. The other data points represent the range of possible block sizes, register counts, and shared memory allocation.

# **Chapter summary**

### **We have explored:**

- Pipeline parallelism

- Dynamic instruction scheduling

- Static instruction scheduling

- Multiple instructions per cycle

- Very long instruction words (VLIW)

- Multi-threading

- Coarse-grain

- Fine-grain

- Simultaneous multithreading (SMT)

- Statically-partitioned multithreading

Vector instructions and SIMD – coming soon SIMT and GPUs – coming soon Multicore – coming soon

## **Extra slides for interest/fun**

Is the "minimum" operator associative?

min(min(X, Y), Z = min(X, min(Y, Z))?

min(X, Y) = if X<Y then X else Y</pre>

$$min(min(10, x), 100) = 100$$

## **Extra slides for interest/fun**

Is the "minimum" operator associative?

- min(min(X, Y), Z = min(X, min(Y, Z))?

- min(X, Y) = if X<Y then X else Y</pre>

All comparisons on NaNs always fail....

min(min(10, NaN), 100) = 100

# Extra slides for interest/fun

Is the "minimum" operator associative?

```

min(min(X, Y), Z = min(X, min(Y, Z))?

```

All comparisons on NaNs always fail....

```

min(X , NaN) = NaN

```

$$\mu \min(NaN, Y) = Y$$

$$\mu \min(\min(X, NaN), Y) = \min(NaN, Y) = Y$$

$$min(X,min(NaN,Y)) = min(X,Y)$$

min(min(10, NaN), 100) = 100