# **NVIDIA Compute**

PTX: Parallel Thread Execution ISA Version 1.0

Release 1.0

#### **Notice**

ALL NVIDIA DESIGN SPECIFICATIONS, REFERENCE BOARDS, FILES, DRAWINGS, DIAGNOSTICS, LISTS, AND OTHER DOCUMENTS (TOGETHER AND SEPARATELY, "MATERIALS") ARE BEING PROVIDED "AS IS." NVIDIA MAKES NO WARRANTIES, EXPRESSED, IMPLIED, STATUTORY, OR OTHERWISE WITH RESPECT TO THE MATERIALS, AND EXPRESSLY DISCLAIMS ALL IMPLIED WARRANTIES OF NONINFRINGEMENT, MERCHANTABILITY, AND FITNESS FOR A PARTICULAR PURPOSE.

Information furnished is believed to be accurate and reliable. However, NVIDIA Corporation assumes no responsibility for the consequences of use of such information or for any infringement of patents or other rights of third parties that may result from its use. No license is granted by implication or otherwise under any patent or patent rights of NVIDIA Corporation. Specifications mentioned in this publication are subject to change without notice. This publication supersedes and replaces all information previously supplied. NVIDIA Corporation products are not authorized for use as critical components in life support devices or systems without express written approval of NVIDIA Corporation.

#### **Trademarks**

NVIDIA, the NVIDIA logo, GeForce, and NVIDIA Quadro are registered trademarks of NVIDIA Corporation. Other company and product names may be trademarks of the respective companies with which they are associated.

#### Copyright

© 2007 by NVIDIA Corporation. All rights reserved.

#### **HISTORY OF MAJOR REVISIONS**

| Version | Date      | Changes                           |  |  |  |

|---------|-----------|-----------------------------------|--|--|--|

| 1.0     | 6/12/2007 | PTX ISA Version 1.0, release 1.0. |  |  |  |

# **Table of Contents**

| Table of | Co   | ntents                                                 | 3  |

|----------|------|--------------------------------------------------------|----|

| Section  | 1. ] | Introduction                                           | 6  |

| 1.1.     | Da   | ta-Parallel Computing using GPUs                       | 6  |

| 1.2.     | Go   | als of PTX                                             | 6  |

| 1.3.     | Th   | e Document's Structure                                 | 7  |

| Section  | 2. I | Programming Model                                      | 8  |

| 2.1.     | Αŀ   | Highly Multithreaded Coprocessor                       | 8  |

| 2.2.     | Th   | read Batching                                          | 8  |

| 2.2.     | .1.  | Cooperative Thread Arrays                              | 8  |

| 2.2.     | .2.  | Grid of Cooperative Thread Arrays                      | 9  |

| Section  | 3. 1 | The Parallel Thread Execution Machine Model            | 11 |

| 3.1.     | A 9  | Set of SIMD Multiprocessors with On-Chip Shared Memory | 11 |

| 3.2.     | Exe  | ecution Model                                          | 12 |

| Section  | 4. 9 | Syntax                                                 | 15 |

| 4.1.     | So   | urce Format                                            | 15 |

| 4.2.     | Со   | mments                                                 | 15 |

| 4.3.     | Sta  | atements                                               | 15 |

| 4.3.     | 1.   | Directive Statements                                   | 16 |

| 4.3.     | 2.   | Instruction Statements                                 | 16 |

| 4.4.     | Ide  | entifiers                                              | 18 |

| 4.5.     | Im   | mediate Constants                                      | 18 |

| 4.5.     | 1.   | Integer Immediate Constants                            | 18 |

| 4.5.     | 2.   | Floating-point Immediate Constants                     | 19 |

| 4.5.     | 3.   | Predicate Immediate Constants                          | 19 |

| 4.5.     | 4.   | Constant Expressions                                   | 19 |

| Section  | 5. 9 | State Spaces, Types, and Variables                     | 20 |

| 5.1.     | Sta  | ate Spaces                                             | 20 |

| 5.1.     | 1.   | Register State Space                                   | 21 |

| 5.1.     | .2.  | Special Register Space                                 | 21 |

| 5.1.     | .3.  | Constant State Space                                   | 21 |

|    | 5.1    | 1.4.        | Global State Space                                   | 22 |

|----|--------|-------------|------------------------------------------------------|----|

|    | 5.1    | 1.5.        | Local State Space                                    | 22 |

|    | 5.1    | 1.6.        | Parameter State Space                                | 22 |

|    | 5.1    | 1.7.        | Shared State Space                                   | 22 |

|    | 5.1    | 1.8.        | Texture State Space                                  | 22 |

|    | 5.1    | 1.9.        | Surface State Space                                  | 23 |

|    | 5.2.   | Typ         | pes                                                  | 23 |

|    | 5.2    | 2.1.        | Fundamental Types                                    | 23 |

|    | 5.2    | 2.2.        | Restricted Use of Sub-word Sizes                     | 24 |

|    | 5.3.   | Var         | iables                                               | 24 |

|    | 5.3    | 3.1.        | Variable Declarations                                | 24 |

|    | 5.3    | 3.2.        | Vectors                                              | 24 |

|    | 5.3    | 3.3.        | Array Declarations                                   | 25 |

|    | 5.3    | 3.4.        | Structures and Unions                                | 25 |

|    | 5.3    | 3.5.        | Initializers                                         |    |

|    |        | 3.6.        | Alignment                                            |    |

| 50 | ection |             | nstruction Operands                                  |    |

|    | 6.1.   | -           | erand Type Information                               |    |

|    | 6.2.   |             | urce Operands                                        |    |

|    | 6.3.   |             | stination Operands                                   |    |

|    | 6.4.   | Usi         | ng Addresses, Arrays, Vectors, Structures and Unions |    |

|    | 6.4    | 4.1.        | Addresses as Operands                                |    |

|    | 6.4    | 4.2.        | Arrays as Operands                                   | 28 |

|    | 6.4    | 4.3.        | Vectors as Operands                                  |    |

|    | 6.4    | <b>1.4.</b> | Structures and Unions as Operands                    | 29 |

|    | 6.4    | 4.5.        | Immediate Values as Operands                         | 29 |

|    | 6.5.   | Typ         | pe Conversion                                        | 30 |

|    | 6.5    | 5.1.        | Scalar Conversions                                   |    |

|    | 6.5    | 5.2.        | Rounding modes                                       | 31 |

|    | 6.5    | 5.3.        | Vector Conversions                                   | 32 |

|    | 6.6.   |             | erand Costs                                          |    |

| 50 | ection | 1 7. I      | nstruction Set                                       | 34 |

|    | 7.1.   |             | mat and Semantics of Instruction Descriptions        |    |

|    | 7.2.   |             | K Instructions                                       |    |

|    | 7.3.   | Pre         | dicated Execution                                    | 34 |

|    | 7.3    | 3.1.        | Comparisons                                          | 35 |

| 7.3.2.     | Manipulating Predicates                                 | . 36 |

|------------|---------------------------------------------------------|------|

| 7.4. Ty    | pe Information for Instructions and Operands            | . 37 |

| 7.5. Di    | ivergence of Threads in Control Constructs              | . 37 |

| 7.6. Se    | emantics                                                | . 38 |

| 7.6.1.     | Machine-specific Semantics of 16-bit Code               | . 38 |

| 7.7. In    | structions                                              | . 39 |

| 7.7.1.     | Arithmetic Instructions                                 | . 39 |

| 7.7.2.     | Comparison and Selection Instructions                   | . 50 |

| 7.7.3.     | Logic and Shift Instructions                            | . 53 |

| 7.7.4.     | Data Movement and Conversion Instructions               | . 57 |

| 7.7.5.     | Texture Instruction                                     | . 61 |

| 7.7.6.     | Control Flow Instructions                               | . 62 |

| 7.7.7.     | Parallel Synchronization and Communication Instructions | 65   |

| 7.7.8.     | Floating-point Instructions                             | . 68 |

| 7.7.9.     | Miscellaneous Instructions                              | . 73 |

| Section 8. | Special Registers                                       | .74  |

| Section 9. | Directives                                              | .78  |

| 9.1. Sp    | pecifying CTAs and Functions                            | . 78 |

| 9.2. De    | ebugging Directives                                     | . 80 |

| 9.3. O     | ther Directives                                         | . 82 |

| Section 10 | ). Release 1.0 Notes                                    | .84  |

# Section 1. Introduction

## 1.1. Data-Parallel Computing using GPUs

This document describes PTX, a low-level *parallel thread execution* virtual machine (VM) and virtual instruction set architecture (ISA). PTX exposes the GPU as a data-parallel computing *device*.

Data-parallel processing maps data elements to parallel processing threads. Many applications that process large data sets such as arrays can use a data-parallel programming model to speed up the computations. Data-parallel mapping is efficient for SIMD, vector, and highly multi-threaded parallel architectures. In 3D rendering, large sets of pixels and vertices are mapped to parallel threads. Similarly, image and media processing applications such as post-processing of rendered images, video encoding and decoding, image scaling, stereo vision, and pattern recognition can map image blocks and pixels to parallel processing threads. Many compute-intensive applications map well to data-parallel processing. In general, all algorithms that can be formulated as parallel computations operating over datasets are good candidates for acceleration by data-parallel processing.

PTX defines a virtual machine and virtual ISA for general purpose parallel thread execution. PTX programs are translated at install time to the target hardware instruction set. The PTX to GPU translator and driver enables NVIDIA GPUs to be used as programmable parallel computers.

### 1.2. Goals of PTX

PTX provides a stable programming model and instruction set for general purpose parallel programming. It is designed to be efficient on NVIDIA GPUs supporting the computation features defined for G80 and subsequent GPUs. High level language compilers for languages such as C and C++ generate PTX instructions, which are optimized for and translated to native target-architecture instructions.

The goals for PTX include the following:

- Provide a stable virtual ISA and VM that spans multiple GPU generations.

- Achieve performance in compiled applications comparable to native GPU performance.

- Provide a machine-independent ISA for C/C++ and other compilers to target.

- Provide a code distribution ISA for application and middleware developers.

- Provide a common source-level ISA for optimizing code generators and translators, which map PTX to specific target machines.

- Programmability facilitate hand-coding of libraries, performance kernels, and architecture tests.

- Scalability VM programming model spans GPU sizes from single unit to many parallel units.

- Provide a relatively low-level ISA and machine model that can be usefully thought of as representing the target GPU architecture.

- VM and virtual ISA will become publicly visible.

- Component of the NV Compute product.

- Compatibility version 1 programs execute on later translators.

- Sufficient quality and usability to evolve into an industry standard.

## 1.3. The Document's Structure

This document is organized in the following way:

Section 2 outlines the programming model.

Section 3 gives an overview of the PTX virtual machine model.

Section 4 describes the basic syntax of the PTX language.

Section 5 describes state spaces, types, and variable declarations.

Section 6 describes instruction operands.

Section 7 describes the instruction set.

Section 8 lists special registers.

Section 9 lists the assembly directives supported in PTX.

Section 10 provides notes for Release 1.0 of PTX Version 1.0.

6/12/2007 9:32:15 AM

# Section 2. Programming Model

## 2.1. A Highly Multithreaded Coprocessor

The GPU is a compute device capable of executing a very high number of threads in parallel. It operates as a coprocessor to the main CPU, or host: In other words, dataparallel, compute-intensive portions of applications running on the host are off-loaded onto the device.

More precisely, a portion of an application that is executed many times, but independently on different data, can be isolated into a function that is executed on the GPU as many different threads. To that effect, such a function is compiled to the PTX instruction set and the resulting kernel is translated at install time to the target GPU instruction set.

# 2.2. Thread Batching

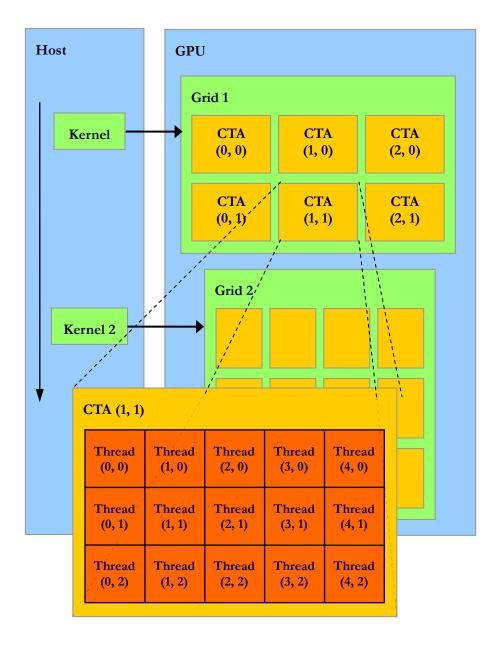

The batch of threads that executes a kernel is organized as a *grid* of *cooperative thread arrays* as described in this section and illustrated in Figure 1.

#### 2.2.1. Cooperative Thread Arrays

The Parallel Thread Execution (PTX) programming model is explicitly parallel – a PTX program specifies the execution of a given thread of a parallel thread array. A *Cooperative Thread Array*, or *CTA*, is an array of threads that execute a kernel concurrently or in parallel.

Threads within a CTA can communicate with each other. To coordinate the communication of the threads within the CTA, one can specify synchronization points, where threads are suspended until they all reach the synchronization point.

Each thread has a unique *thread id (tid)* within the CTA. Programs use a data parallel decomposition to partition inputs, work, and results across the threads of the CTA. Each CTA thread uses its tid to determine its assigned role, assign specific input and output position, compute addresses, and select work to perform. The tid is a 3-component vector, *tid.0*, *tid.1*, and *tid.2*, that specifies the thread's position within a 1D, 2D, or 3D CTA. Alternate component names are *tid.x*, *tid.y*, and *tid.z*. Each tid component ranges from 0 up to the number of thread id's in that CTA dimension.

Each CTA has a a 1D, 2D, or 3D shape, specified by a 3-component vector, *ntid*, which specifies the number of threads in each CTA dimension. The ntid components are accessible as *ntid*.0, *ntid*.1, and *ntid*.2.

Threads within a CTA execute in SIMD fashion in groups called *warps*. A warp is a maximal subset of threads from a single CTA, such that the threads execute the same

instructions at the same time. Threads within a warp are sequentially numbered. The warp size is a machine-dependent constant. Typically, a warp has 16 or 32 threads. Some applications may be able to maximize performance with knowledge of the warp size, so PTX includes a run-time immediate constant, WARP\_SZ, which may be used in any instruction where an immediate operand is allowed.

#### 2.2.2. Grid of Cooperative Thread Arrays

There is a maximum number of threads that a CTA can contain. However, CTAs that execute the same kernel can be batched together into a *grid* of CTAs, so that the total number of threads that can be launched in a single kernel invocation is very large. This comes at the expense of reduced thread communication and synchronization, because threads in different CTAs cannot communicate and synchronize with each other.

Multiple CTAs may execute concurrently and in parallel, or sequentially, depending on the platform. Each CTA has a unique CTA id (ctaid) within a grid of CTAs. Each grid of CTAs has a 1D, 2D, or 3D shape specified by the parameter nctaid. Each grid also has a unique temporal grid id (gridid). Threads may read and use these values through predefined, read-only special registers %tid, %ntid, %ctaid, %nctaid, and %gridid.

Figure 1: Thread Batching

The host issues a succession of kernel invocations to the device. Each kernel is executed as a batch of threads organized as a grid of CTAs.

# Section 3. The Parallel Thread Execution Machine Model

# 3.1. A Set of SIMD Multiprocessors with On-Chip Shared Memory

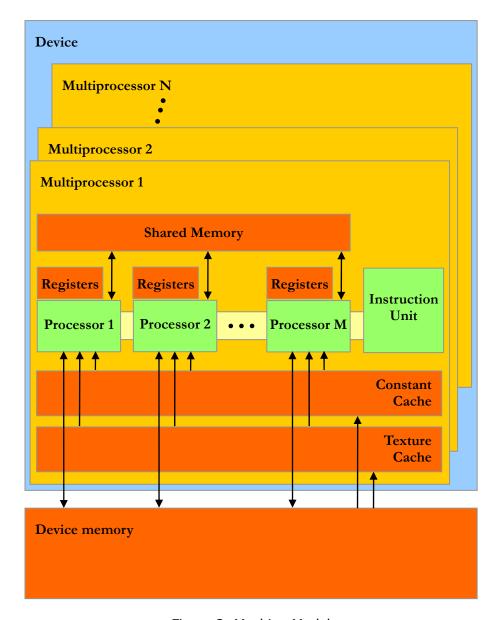

The PTX machine model is implemented as a set of multiprocessors as illustrated in Figure 2. Each multiprocessor has a Single Instruction, Multiple Data architecture (SIMD): At any given clock cycle, each processor of the multiprocessor executes the same instruction, but operates on different data.

Both the host and the device maintain their own local memory, referred to as *host memory* and *device memory*, respectively. The device memory may be mapped and read or written by the host, or, for more efficient transfer, copied from the host memory through optimized API calls that utilize the device's high-performance Direct Memory Access (DMA) engine.

Each multiprocessor has on-chip memory of the four following types:

- One set of local 32-bit registers per processor,

- *Shared memory* that is shared by all the processors,

- A read-only *constant cache* that is shared by all the processors and speeds up reads from the constant memory, which is a read-only region of the device memory,

- A read-only texture cache that is shared by all the processors and dedicated to texture sampling.

Figure 2: Machine Model

A set of SIMD multiprocessors with on-chip shared memory.

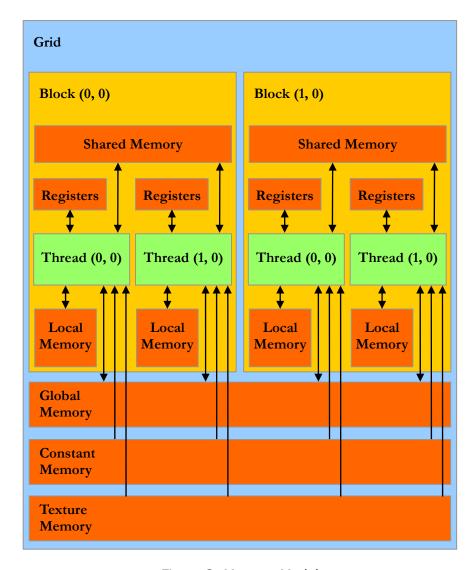

# 3.2. Execution Model

A grid of CTAs is executed on the device by executing one or more CTAs on each multiprocessor using time slicing: Each CTA is split into SIMD groups of threads called *warps*; each of these warps contains the same number of threads, called the *warp size*, and is executed by the multiprocessor in a SIMD fashion; a thread scheduler periodically switches from one warp to another to maximize the use of the multiprocessor's computational resources.

The way a CTA is split into warps is always the same; each warp contains threads of consecutive, increasing thread indices with the first warp containing thread 0.

A CTA is processed by only one multiprocessor, so that threads within a CTA can use the on-chip shared memory to efficiently share data among them. More precisely, threads can perform general reads from and writes to the on-chip shared memory through a per-CTA shared memory partition and coordinate these memory accesses through synchronization mechanisms.

A multiprocessor can process several CTAs concurrently by partitioning its resources (e.g. registers and shared memory) among them.

Threads can access several other memory partitions:

- Threads can perform general cached reads from the constant memory through a per-grid constant memory partition.

- Threads can perform general non-cached reads from and writes to the device memory through two device memory partitions: a per-thread *local memory partition* and a per-grid *global memory partition*.

- At last, another way to perform general cached reads from the device memory is through texture sampling.

This memory model is illustrated in Figure 3.

The issue order of the CTAs within a grid is not defined and there is no synchronization mechanism between CTAs, so threads from two different CTAs of the same grid cannot safely communicate with each other through the device memory.

Figure 3: Memory Model

Shared memory and registers are on chip. Texture memory, constant memory, local memory, and global memory are in device memory. Reads from texture memory and constant memory are cached. Reads from and writes to local and global memory are not cached.

# Section 4. Syntax

PTX programs are a collection of text source files. PTX source files have an assembly-language style syntax with instruction operation codes and operands. Pseudo-operations specify symbol and addressing management. The **ptxas** program assembles PTX source files to produce corresponding binary object files.

#### 4.1. Source Format

Source files are ASCII text. Lines are separated by the newline character ('\n').

All whitespace characters are equivalent; whitespace is ignored except for its use in separating tokens in the language.

The C preprocessor **cpp** may be used to process PTX source files. Lines beginning with # are preprocessor directives. The following are common preprocessor directives:

```

#include, #define, #if, #ifdef, #else, #endif, #line, #file

```

"C: A Reference Manual" by Harbison and Steele provides a good description of the C preprocessor.

PTX is case sensitive and uses lowercase for keywords.

Each PTX file must begin with a .version directive specifying the PTX language version, followed by a .target directive specifying the target architecture assumed. See Section 9 for a more information on these directives.

## 4.2. Comments

Comments in PTX follow C/C++ syntax, using non-nested /\* and \*/ for comments that may span multiple lines, and using // to begin a comment that extends to the end of the current line.

Comments in PTX are treated as whitespace.

## 4.3. Statements

A PTX statement is either a directive or an instruction. Statements begin with an optional label and end with a semicolon.

Examples:

#### 4.3.1. Directive Statements

Directive keywords begin with a dot, so no conflict is possible with user-defined identifiers. The directives in PTX are listed in Table 1 and described in Section 9.

| .byte   | .func   | .reg     | .target  |

|---------|---------|----------|----------|

| .const  | .global | .section | .tex     |

| .entry  | .local  | .shared  | .version |

| .extern | .loc    | .sreg    | .visible |

| .file   | .param  | .surf    |          |

Table 1: Directives

#### 4.3.2. Instruction Statements

Instructions are formed from an instruction opcode followed by a comma-separated list of zero or more operands, and terminated with a semicolon. Operands may be register variables, constant expressions, address expressions, or label names. Instructions have an optional guard predicate which controls conditional execution. The guard predicate follows the optional label and precedes the opcode, and is written as **@p**, where p is a predicate register. The guard predicate may be optionally negated, written as **@!p**.

The destination operand is first, followed by source operands.

Instruction keywords are listed in Table 2. All instruction keywords are reserved tokens in PTX.

| abs   | div     | max    | ret   | sub  |

|-------|---------|--------|-------|------|

| add   | dot     | membar | rsqrt | tex  |

| and   | ex2     | min    | sad   | trap |

| atom  | exit    | mov    | selp  | vote |

| bar   | extract | mul    | set   | vred |

| bra   | frc     | mul24  | setp  | xor  |

| brkpt | insert  | neg    | shl   |      |

| call  | ld      | nop    | shr   |      |

| cnot  | lg2     | not    | sin   |      |

| cos   | mad     | or     | slct  |      |

| cross | mad24   | rcp    | sqrt  |      |

| cvt   | mag     | rem    | st    |      |

Table 2: Reserved Instruction Keywords

### 4.4. Identifiers

User-defined identifiers follow extended C++ rules: they start with an alphabetic character, underscore, dollar sign, or percentage sign ([A-Za-z\_\$\\$]) and are followed by zero or more alphanumeric, underscore, or dollar sign characters ([A-Za-z\_\$]).

Many high-level languages such as C and C++ follow similar rules for identifier names, except that the percentage sign is not allowed. PTX allows the percentage sign as the first character of an identifier. The percentage sign can be used to avoid name conflicts, e.g. between user-defined variable names and compiler-generated names.

PTX predefines a small number of special registers that begin with the percentage sign, listed in Table 3.

| %ctaid  | %clock  | %pm2 |

|---------|---------|------|

| %gridid | %physid | %pm3 |

| %nctaid | %pm0    | %tid |

| %ntid   | %pm1    |      |

Table 3: Predefined identifiers

### 4.5. Immediate Constants

Immediate constants in PTX are restricted to integer and floating-point types.

#### 4.5.1. Integer Immediate Constants

Integer immediate constants may be written in decimal, hexadecimal, octal, or binary notation.

Decimal constants begin with a nonzero digit followed by zero or more digits (0-9).

Hexadecimal constants begin with **0x** or **0X** followed by one or more hex digits (from the set [**0-9a-fA-F**]).

Octal constants begin with zero **0** followed by zero or more octal digits (**0-7**).

Binary constants begin with **0b** or **0B** followed by one or more binary digits (**01**).

### 4.5.2. Floating-point Immediate Constants

Floating-point immediate constants may be written with an optional decimal point and an optional signed exponent. Unlike C and C++, there is no suffix letter to specify size (e.g. float or double).

PTX includes a second representation of floating-point constants, where the exact machine representation is given as a hexadecimal constant. For 64-bit floating point values, the constant begins with **0d** or **0D** followed by 16 hex digits. For 32-bit floating point values, the constant begins with **0f** or **0F** followed by 8 hex digits.

#### 4.5.3. Predicate Immediate Constants

Predicate immediate constants for the Boolean values **TRUE** and **FALSE** are written as binary digits **1** and **0**, respectively.

#### 4.5.4. Constant Expressions

Constant expressions are evaluated at compile time to form simple values for use in immediate operands and addressing expressions. Both integer and floating-point constant expressions are supported, however, note that floating-point constant expressions may evaluate to a different value than would be computed on the target architecture, since the compiler may evaluate the expression using greater precision than the target architecture.

Constant expressions are formed from lexical constants, basic arithmetic operators (addition, subtraction, multiplication, division), and parentheses. Integer constant expressions may include remainder (%), shift operators (<< and >>), and logical operators (&, |, and  $^{\wedge}$ ).

The meaning of operators in PTX is the same as in C or C++.

# Section 5. State Spaces, Types, and Variables

While the specific resources available in a given target GPU will vary, the kinds of resources will be common across platforms, and these resources are abstracted in PTX through state spaces and data types.

# 5.1. State Spaces

A *state space* is a storage area with particular characteristics. All variables reside in some state space. The characteristics of a state space include its size, addressability, access speed, access rights, and level of sharing between threads.

The state spaces defined in PTX are a byproduct of parallel programming and graphics programming. The list of state spaces is shown in Table 4, and properties of state spaces are shown in Table 5.

| Name    | Description                                                   |  |  |  |

|---------|---------------------------------------------------------------|--|--|--|

| .reg    | Registers, fast.                                              |  |  |  |

| .sreg   | Special registers. Read-only; pre-defined; platform-specific. |  |  |  |

| .const  | Per-CTA, shared, read-only memory.                            |  |  |  |

| .global | Global memory, shared by all threads.                         |  |  |  |

| .local  | Local memory, private to each thread.                         |  |  |  |

| .param  | User parameters for a program, available at CTA entry.        |  |  |  |

| .shared | Addressable memory shared between threads in 1 CTA.           |  |  |  |

| .surf   | Global surface memory.                                        |  |  |  |

| .tex    | Global texture memory.                                        |  |  |  |

Table 4: State spaces

| Name    | Addressible                     | Initializable | Access | Sharing    |  |

|---------|---------------------------------|---------------|--------|------------|--|

| .reg    | No                              | No            | R/W    | per-thread |  |

| .sreg   | No                              | No            | RO     | per-CTA    |  |

| .const  | Yes                             | Yes           | RO     | per-grid   |  |

| .global | Yes                             | Yes           | R/W    | Context    |  |

| .local  | Yes                             | No            | R/W    | per-thread |  |

| .param  | Yes                             | No            | RO     | per-grid   |  |

| .shared | Yes                             | No            | R/W    | per-CTA    |  |

| .surf   | via LD/ST, SURF<br>instructions | Yes           | R/W    | Context    |  |

| .tex    | via TEX instruction             | Yes           | RO     | Context    |  |

Table 5: Properties of state spaces

#### 5.1.1. Register State Space

Registers (.reg state space) are fast storage locations. The number of registers is limited, and will vary from platform to platform. When the limit is exceeded, register variables will be spilled to memory, causing changes in performance. For each architecture, there is a recommended maximum number of registers to use.

Registers may be typed (signed integer, unsigned integer, floating point, predicate) or untyped. Register size is restricted; aside from predicate registers which are 1-bit, registers have a width of 16-, 32-, or 64-bits.

Registers differ from the other state spaces in that they are not fully addressable, i.e., it is not possible to refer to the address of a register.

Registers may have alignment boundaries required by multi-word loads and stores.

#### 5.1.2. Special Register Space

The special register (.sreg) state space holds predefined, platform-specific registers, such as grid, CTA, and thread parameters, clock counters, and performance monitoring registers. All special registers are predefined.

#### 5.1.3. Constant State Space

The constant (.const) state space is a read-only memory, initialized by the host. The size may be limited, and there are typically many *banks* of constant memory, denoted by an integer index. The size and number of banks are listed in the appendix for different hardware.

21

#### 5.1.4. Global State Space

The global (.global) state space is memory that is accessible by all threads in a context. It is the mechanism by which different CTAs and different grids can communicate. Use ld.global, st.global, atom.global, and red.global to access global variables.

For any thread in a context, all addresses are in global memory are shared.

Global memory is not sequentially consistent. Consider the case where one thread executes the following two assignments:

```

a = a + 1;

b = b - 1;

```

If another thread sees the variable *b* change, the store operation updating *a* may still be in flight. This reiterates the kind of parallelism available in machines that run PTX. Threads must be able to do their work without waiting for other threads to do theirs, as in lock-free and wait-free style programming.

### 5.1.5. Local State Space

The local state space (local) is private memory for each thread to keep its own data. It is typically standard memory with cache. The size is limited, as it must be allocated on a per-thread basis. Use ld.local and st.local to access local variables.

#### 5.1.6. Parameter State Space

The parameter (.param) state space provides addressable user parameters to CTAs. User parameters begin at address zero, and the address space is shared across CTAs within a grid.

The location of parameter space is implementation specific. For example, in some implementations, parameter space resides in global memory. No access protection is provided between parameter and global space in this case.

#### 5.1.7. Shared State Space

The shared (.shared) state space is a per-CTA region of memory for threads in a CTA to share data. An address in shared memory can be read and written by any thread in a CTA. Use ld.shared and st.shared to access shared variables.

Shared memory typically has some optimizations to support the sharing. One example is broadcast; where all threads read from the same address. Another is sequential access from sequential threads.

#### 5.1.8. Texture State Space

The texture (.tex) state space is global memory for the texture instructions. It is shared by all threads in a context.

The GPU hardware has a fixed number of texture bindings that can be accessed within a single program (typically 128). The .tex[i] directive will bind the named texture memory variable to the hardware texture id 'i'. If no id number is given, PTX will assign

texture id's sequentially, beginning with zero. Multiple names may be bound to the same physical texture id. An error is generated only if the texture id assigned is out of the physical texture id range (e.g., 0..127).

Texture memory is read-only.

#### Example:

#### 5.1.9. Surface State Space

The surface (.surf) state space is similar to global memory, but is 2D in nature. It takes a 2D address (*i* and *j* components), and with respect to cache, spatial locality generally works well in a 2D neighborhood. This allows tiled decompositions to perform quite well.

## 5.2. Types

#### 5.2.1. Fundamental Types

In PTX, the fundamental types reflect the native data types supported by the target architectures. A fundamental type specifies both a basic type and a size. Register variables are always of a fundamental type, and instructions operate on these types. The same type-size specifiers are used for both variable definitions and for typing instructions, so their names are intentionally short.

The following table lists the fundamental type specifiers for each basic type:

| Basic Type       | Fundamental Type Specifiers |  |  |  |

|------------------|-----------------------------|--|--|--|

| Signed integer   | .s8, .s16, .s32, .s64       |  |  |  |

| Unsigned integer | .u8, .u16, .u32, .u64       |  |  |  |

| Floating-point   | .f16, .f32, .f64            |  |  |  |

| Bits (untyped)   | .b8, .b16, .b32, .b64       |  |  |  |

| Predicate        | .pred                       |  |  |  |

Most instructions have one or more type specifiers, needed to fully specify instruction behavior. Operand types and sizes are checked against instruction types for compatibility.

Two fundamental types are compatible if they have the same basic type and are the same size. Signed and unsigned integer types are compatible if they have the same size. The bit-size type is compatible with any fundamental type having the same size.

In principle, all variables could be declared using only bit-size types, but typed variables enhance program readability and allow for better operand type checking.

#### 5.2.2. Restricted Use of Sub-word Sizes

The .u8 and .s8 types are restricted to **ld**, **st**, and **cvt** instructions. The **ld** and **st** instructions also accept .b8 type. Byte-size integer load instructions zero- or sign-extended the value to the size of the destination register.

The .f16 floating-point type is allowed only in conversions to and from .f32 and .f64 types. All floating-point instructions operate only on .f32 and .f64 types.

#### 5.3. Variables

In PTX, a variable declaration describes both the variable's type and its state space. In addition to fundamental types, PTX supports types for aggregate objects such as vectors, arrays, structures and unions.

#### 5.3.1. Variable Declarations

All storage for data is specified with variable declarations. Every variable must reside in one of the state spaces enumerated in the previous section.

A variable declaration names the space in which the variable resides, its type and size, its name, an optional array size, an optional initializer, and an optional fixed address for the variable.

Examples:

```

.global .u32 loc;

.reg .s32 i = 0;

.shared .f32 bias[] = {-1.0, 1.0};

.local .u8 bg[4] = {0, 0, 0, 0};

.reg .v3 .f32 accel;

.struct float4 { .f32[4] v };

.global float4 coord;

```

Note that texture and surface variables do not have an associated type and size.

#### 5.3.2. Vectors

Limited-length vector types are supported. Vectors of length 2, 3, and 4 of any fundamental type can be declared by prefixing the type with .v2, .v3, or .v4. Vectors must be based on a fundamental type, and they may reside in the register space.

Examples:

```

.global .v4 .f32 V; // a length-4 vector of floats

```

```

.shared .v2 .u16 uv;  // a length-2 vector of unsigned ints

.reg .v4 .pred vpred;  // a vector of predicates registers

```

### 5.3.3. Array Declarations

Array declarations are provided to allow the programmer to reserve space. To declare an array, the variable name is followed with dimensional declarations similar to fixed-size array declarations in C. The size of the dimension is either a constant expression, or is left empty, being determined by an array initializer. Here are some examples:

```

.local .u16 kernel[19][19];

.shared .u8 mailbox[128];

.shared .s32 offset[][] = { {-1, 0}, {0, -1}, {1, 0}, {0, 1} };

```

The size of the array specifies how many elements should be reserved. For the *kernel* declaration above, 19\*19 (361) halfwords are reserved (722 bytes).

#### 5.3.4. Structures and Unions

A structure definition specifies a sequence of fields (consisting of a type/size and a name) as a block of memory. This is analogous to the structures in C. Once defined, the structure can be used as a type designator in subsequent variable declarations.

Example:

```

.struct somestruct { .s32 i; .s32 j; .f32 x; .f32 y; };

.global somestruct p;

.reg .b32 ptr;

...

ld.s32 r0, [p.x];

mov.b32 ptr, p; // get address of structure p

```

Unions definitions use the same syntax as struct definitions, with the keyword **.struct** replaced by **.union**. The difference between a struct and a union is that in a struct, the fields are laid out sequentially in memory, while in a union, the fields all use the same memory. Unions provide a way to reuse memory in a relatively type-safe manner. Here is an example that provides storage for a float or an integer:

```

.union intOrFloat { .s32 i; .f32 f; };

```

Structure and union declarations may be nested. The shortcut syntax of C++ with anonymous unions is also supported.

#### 5.3.5. Initializers

All declarations may specify an initial value for the variable being declared (including predicates). The initializers follow the conventions of C/C++, where the variable name is followed by an equals sign and the value or values for the initial values of the variable. A scalar takes a single value; while vectors and arrays take nested lists of values inside of curly braces (the nesting matches the dimensionality of the declaration). Structures take a list of values that matches the fields in a structure.

Examples:

```

.global .s32 n = 10;

.shared .f16 blur_kernel[][]

= {{.05,.1,.05},{.1,.4,.1},{.05,.1,.05}};

.global .v3 .u8 rgb[3] = {{1, 0, 0}, {0, 1, 0}, {0, 0, 1}};

```

Initializers for thread-private memory all initialize their variables to the same value. There is no syntax for per-thread initializers.

#### 5.3.6. Alignment

Byte alignment of storage for all addressable variables can be specified in the variable declaration. Alignment is specified using an optional align *byte\_count* specifier immediately following the space-state specifier. The variable will be aligned to an address which is an integer multiple of *byte\_count*. For arrays, structures, and unions, alignment specifies the address alignment for the starting address of the entire structure, not for individual elements.

#### Examples:

```

// allocate array at 4-byte aligned address. Elements are bytes.

.const .align 4 .b8 bar[8] = {0,0,0,0,2,0,0,0};

```

# Section 6. Instruction Operands

## 6.1. Operand Type Information

All operands in instructions have a known type from their declarations. Each operand type must be compatible with the type determined by the instruction template and instruction type. There is no automatic conversion between types.

The bit-size type is compatible with every type having the same size. Integer types of a common size are compatible with each other. Operands having type different from but compatible with the instruction type are silently cast to the instruction type.

# 6.2. Source Operands

The source operands are denoted in the instruction descriptions by the names **a**, **b**, and **c**. PTX describes a load-store machine, so operands for ALU instructions must all be in variables declared in the **.reg** register state space. For most operations, the sizes of the operands must be consistent.

The **cvt** (convert) instruction takes a variety of operand types and sizes, as its job is to convert from nearly any data type to any other data type (and size).

The **ld**, **st**, **mov**, and **cvt** instructions copy data from one location to another. Instructions **ld** and **st** move data from/to addressable state spaces to/from registers. The **mov** instruction copies data between registers.

Most instructions have an optional predicate guard that controls conditional execution, and a few instructions have additional predicate source operands. Predicate operands are denoted by the names **p**, **q**, **r**, **s**.

# 6.3. Destination Operands

PTX instructions that produce a single result store the result in the field denoted by **d** (for destination) in the instruction descriptions. The result operand can be any declared variable, array element, structure/union member, vector or vector element.

6/12/2007 9:32:15 AM

# 6.4. Using Addresses, Arrays, Vectors, Structures and Unions

Using scalar variables as operands is straightforward. The interesting capabilities begin with pointers, composite structures, and arrays.

#### 6.4.1. Addresses as Operands

Address arithmetic is performed using integer arithmetic and logical instructions. Examples include pointer arithmetic and pointer comparisons. All addresses and address computations are byte-based; there is no support for C-style pointer arithmetic.

The mov instruction can be used to move the address of a variable into a pointer. Load and store operations move data between registers and locations in addressable state spaces. The syntax is similar to that used in many assembly languages, where scalar variables are simply named and addresses are de-referenced by enclosing the address expression in square brackets. Address expressions include variable names, address registers, address register plus byte offset, and immediate address expressions which evaluate at compile-time to a constant address.

Here are a few examples:

```

.shared .u16 x;

.reg .u16 r0;

.global .v4 .f16 V;

.reg .v4 .f16 W;

.const .s32 tbl[256];

.reg .b32 p;

.reg .s32 q;

ld.u16 r0,[x];

ld.v4.f16 W, [V];

ld.s32 q, [tbl+12];

mov.b32 p, tbl;

```

#### 6.4.2. Arrays as Operands

Arrays of all types can be declared, and the identifier becomes an address constant in the space where the array is declared. The size of the array is a constant in the program.

Array elements can be accessed using an explicitly calculated byte address, or by indexing into the array using square-bracket notation. The expression within square brackets is either a constant integer, a register variable, or a simple "register with constant offset" expression, where the offset is a constant expression that is either added or subtracted from a register variable. If more complicated indexing is desired, it must be written as an address calculation prior to use. Examples are

#### 6.4.3. Vectors as Operands

Vectors can be treated as a collection of elements simply by naming them. Vector variables can typically replace scalar variables in most PTX instructions, and the meaning is to perform the operation on an element-by-element basis.

```

.reg .v4 .f16 v1, v2, v3;

add.v4.s32 v3, v2, v1;

```

Vector elements can be extracted from the vector with the suffixes .0, .1, .2, and .3 or .x, .y, .z and .w suffixes, as well as the typical color fields .r, .g, .b and .a.

Vectors can be swizzled or reordered with swizzling suffixes, which are a combination of the digits or characters that represent the elements of a vector (0123, xyzw, rgba). The swizzling suffixes allow arbitrary duplication and reordering of vector elements. Swizzling is allowed only in **mov** instructions, and the source and destination must be distinct

A brace-enclosed list is used for pattern matching to pull apart vectors. Wide loads and stores can be specified to multiple targets using vector loads, specifying multiple scalars within the brace-enclosed list. Here are some examples:

```

.reg .v3 .f32 V;

.reg .f32 a, b, c;

mov.v3.f32 {a,b,c}, V;

```

Vector loads and stores can be used to implement wide loads and stores, which may improve memory performance. The registers in the load/store operations can be a vector, or a brace-enclosed list of similarly typed scalars. Here is an example:

```

ld.v4.f32 {a,b,c,d}, [Vmem];

```

Elements in a brace-enclosed vector, say {Ra, Rb, Rc, Rd}, correspond to extracted elements as follows:

```

Ra = V.0 = V.x = V.r

Rb = V.1 = V.y = V.g

Rc = V.2 = V.z = V.b

Rd = V.3 = V.w = V.a

```

### 6.4.4. Structures and Unions as Operands

Structures and unions can only access their members; there are no instructions that take entire structures as operands.

#### 6.4.5. Immediate Values as Operands

Immediate values (or constants) can be used in most instructions. Only one immediate operand is permitted in an instruction. In ALU instructions, it is typically the **b** or **c** operand. In load and store instructions, an immediate offset to a register or an immediate absolute address is permitted. In instruction with only one source operand, the source operand may be an immediate. The size of the immediate value may be specified with a type suffix like .u16, and defaults to the size of the instruction source operand.

For directly specifying IEEE-752 single and double precision floating point numbers, a hexadecimal value may be used as an immediate operand in floating point operations. The immediate value syntax is as follows:

```

0[fF]{hexdigit}{8} // single-precision floating point

0[dD]{hexdigit}{16} // double-precision floating point

```

#### Example:

```

mov.f32 $f3, 0F3f800000; // 1.0

```

This format may also be used when initializing variables.

# 6.5. Type Conversion

All operands to all arithmetic, logic, and data movement instruction must be of the same type and size, except for operations where changing the size and/or type is part of the definition of the instruction. Operands of different sizes or types must be converted prior to the operation.

#### 6.5.1. Scalar Conversions

Table 6 below shows what precision and format the **cvt** instruction uses given operands of differing types. For example, if a **cvt.s32.u16** instruction is given a **u16** source operand and **s32** as a destination operand, the **u16** is zero-extended to **s32**.

Some of the above conversions are available at no cost (sign-extension, zero-extension, chop), while others are not (x2y conversions). The general rule is that that for integers, there is no cost converting between different sizes. All other conversions may require computation.

Conversions to floating-point that are beyond the range of floating-point numbers are represented with the maximum floating-point value (IEEE Inf for  $\mathbf{f32}$  and  $\mathbf{f64}$ , and  $\sim 131,000$  for  $\mathbf{f16}$ ).

|               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Destination Format |                   |      |      |                   |                   |      |      |     |     |     |

|---------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|-------------------|------|------|-------------------|-------------------|------|------|-----|-----|-----|

|               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | s8                 | s16               | s32  | s64  | u8                | u16               | u32  | u64  | f16 | f32 | f64 |

|               | s8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | -                  | sext              | sext | sext | -                 | sext              | sext | sext | s2f | s2f | s2f |

|               | s16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Chop <sup>1</sup>  | -                 | sext | sext | chop <sup>1</sup> | -                 | sext | sext | s2f | s2f | s2f |

|               | s32                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Chop <sup>1</sup>  | chop <sup>1</sup> | -    | sext | chop <sup>1</sup> | chop <sup>1</sup> | -    | sext | s2f | s2f | s2f |

| <b>#</b>      | s64                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Chop <sup>1</sup>  | chop <sup>1</sup> | chop | -    | chop <sup>1</sup> | chop <sup>1</sup> | chop | -    | s2f | s2f | s2f |

| Source Format | u8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | -                  | zext              | zext | zext | -                 | zext              | zext | zext | u2f | u2f | u2f |

| e Fc          | u16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Chop <sup>1</sup>  | -                 | zext | zext | chop <sup>1</sup> | -                 | zext | zext | u2f | u2f | u2f |

| onro          | u32                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Chop <sup>1</sup>  | chop <sup>1</sup> | -    | zext | chop <sup>1</sup> | chop <sup>1</sup> | -    | zext | u2f | u2f | u2f |

| Š             | u64                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Chop <sup>1</sup>  | chop <sup>1</sup> | chop | -    | chop <sup>1</sup> | chop <sup>1</sup> | chop | -    | u2f | u2f | u2f |

|               | f16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | f2s                | f2s               | f2s  | f2s  | f2u               | f2u               | f2u  | f2u  | -   | f2f | f2f |

|               | f32                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | f2s                | f2s               | f2s  | f2s  | f2u               | f2u               | f2u  | f2u  | f2f | -   | f2f |

|               | f64                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | f2s                | f2s               | f2s  | f2s  | f2u               | f2u               | f2u  | f2u  | f2f | f2f | -   |

| No            | sext = sign extend; zext = zero-extend; chop = keep only low bits that fit; s2f = signed-to-float; f2s = float-to-signed; u2f = unsigned-to-float; f2u = float-to-unsigned; f2f = float-to-float;  1 If the destination register is wider than the destination format, the result is extended to the destination register width after chopping. The type of extension (sign or zero) is based on the destination format. For example, cvt.s16.u32 targeting a 32-bit register will first chop to 16-bits, then sign-extend to 32-bits. |                    |                   |      |      |                   |                   |      |      |     |     |     |

Table 6: Conversions

# 6.5.2. Rounding modes

Conversion instructions may specify a rounding mode. In PTX, there are four integer rounding modes and four floating-point rounding modes. The following tables summarize the rounding modes.

| Mode | Description                                   |  |  |  |

|------|-----------------------------------------------|--|--|--|

| .rn  | mantissa LSB rounds to nearest even           |  |  |  |

| .rz  | mantissa LSB rounds towards zero              |  |  |  |

| .rm  | mantissa LSB rounds towards negative infinity |  |  |  |

| .rp  | mantissa LSB rounds towards positive infinity |  |  |  |

Table 7: Floating-point Rounding Modes

| Mode | Description                                                                                     |  |

|------|-------------------------------------------------------------------------------------------------|--|

| .rni | round to nearest integer, choosing even integer if source is equidistance between two integers. |  |

| .rzi | round to nearest integer in the direction of zero                                               |  |

| .rmi | round to nearest integer in direction of negative infinity                                      |  |

| .rpi | round to nearest integer in direction of positive infinity                                      |  |

Table 8: Integer Rounding Modes

#### 6.5.3. Vector Conversions

Conversions between scalar values and vector values are supported, allowing operations like adding the scalar value 1 to a vector. Scalar values are spread out to match the size of the vector. Short vectors are zero-extended to longer vectors, and long vectors are truncated when assigned to shorter vectors. The table below describes the conversions, where s is a scalar value and v is a vector.

| Scalar-Vector<br>Vector-Vector<br>Conversions |        | Destination |            |                 |                    |

|-----------------------------------------------|--------|-------------|------------|-----------------|--------------------|

|                                               |        | scalar      | v2         | <b>v</b> 3      | v4                 |

|                                               | scalar | -           | [s, s]     | [s, s, s]       | [s, s, s, s]       |

| Source                                        | v2     | v.0         | -          | [v.0, v.1, 0]   | [v.0, v.1, 0, 0]   |

|                                               | v3     | v.0         | [v.0, v.1] | -               | [v.0, v.1, v.2, 0] |

|                                               | v4     | v.0         | [v.0, v.1] | [v.0, v.1, v.2] | -                  |

Vector immediate values are specified similarly to aggregate initialization, but are not necessary unless the values are different (scalars are spread automatically). Some examples are shown below.

```

.global .v3 .f32 V;

add.v3.f32 V, V, 1;

cross.v3.f32 V, V, {0, 1, 0};

```

# 6.6. Operand Costs

Operands from different state spaces will affect the speed of an operation. Registers are fastest, while global memory is slowest. Much of the delay to memory can be hidden in a number of ways. The first is to have multiple threads of execution so that the hardware can issue a memory operation and then switch to other execution. Another way to hide latency is to issue the load instructions as early as possible, as execution is

not blocked until the desired result is used in a subsequent (in time) instruction. The register in a store operation is available much more quickly. Table 9 gives estimates of the costs of using different kinds of memory.

| Space     | Time         | Notes                                       |

|-----------|--------------|---------------------------------------------|

| Register  | 0            |                                             |

| Shared    | 0            |                                             |

| Constant  | 0            | Amortized cost is low, first access is high |

| Local     | > 100 clocks |                                             |

| Parameter | 0            |                                             |

| Immediate | 0            |                                             |

| Global    | > 100 clocks |                                             |

| Texture   | > 100 clocks |                                             |

| Surface   | > 100 clocks |                                             |

Table 9: Cost estimates for accessing state-spaces

# Section 7. Instruction Set

# 7.1. Format and Semantics of Instruction Descriptions

This section describes each PTX instruction. In addition to the name and the format of the instruction, the semantics are described, followed by some examples that attempt to show several possible instantiations of the instruction.

#### 7.2. PTX Instructions

PTX instructions generally have from zero to four operands, plus an optional guard predicate appearing after an '@' symbol to the left of the opcode:

```

@P opcode;

@P opcode A;

@P opcode D, A;

@P opcode D, A, B;

@P opcode D, A, B, C;

```

For instructions that create a result value, the D operand is the destination operand, while A, B, and C are the source operands.

The setp instruction writes two destination registers. We use a '|' symbol to separate multiple destination registers.

```

setp.s32.lt p | q, a, b; // p = (a < b); q = !(a < b);

```

For some instructions the destination operand is optional. A "bit bucket" operand denoted with an underscore ('\_') may be used in place of a destination register.

## 7.3. Predicated Execution

In PTX, predicate registers are virtual and have .pred as the type specifier. So, predicate registers can be declared as

```

.reg .pred p, q, r

```

All instructions have an optional "guard predicate" which controls conditional execution of the instruction. The syntax to specify conditional execution is to prefix an instruction with "@[!]p", where p is a predicate variable, optionally negated. Instructions without a guard predicate are executed unconditionally.

Predicates are most commonly set as the result of a comparison performed by the SETP instruction.

As an example, consider the high-level code

This can be written in PTX as

```

setp.lt.s32 p, i, n; // p = (i < n)

@p add.s32 j, j, 1; // if i < n, add 1 to j

```

To get a conditional branch or conditional function call, use a predicate to control the execution of the branch or call instructions. To implement the above example as a true conditional branch, the following PTX instruction sequence might be used:

## 7.3.1. Comparisons

#### 7.3.1.1. Integer and Bit-Size Comparisons

The signed integer comparisons are the traditional **eq** (equal), **ne** (not-equal), **lt** (less-than), **le** (less-than-or-equal), **gt** (greater-than), and **ge** (greater-than-or-equal). The unsigned comparisons are **eq**, **ne**, **lo** (lower), **ls** (lower-or-same), **hi** (higher), and **hs** (higher-or-same). The bit-size comparisons are **eq** and **ne**; ordering comparisons are not defined for bit-size types. The following table shows the operators for signed integer, unsigned integer, and bit-size types.

| Meaning | Signed<br>Operator | Unsigned<br>Operator | Bit-Size<br>Operator |

|---------|--------------------|----------------------|----------------------|

| a == b  | EQ                 | EQ                   | EQ                   |

| a != b  | NE                 | NE                   | NE                   |

| a < b   | LT                 | LO                   |                      |

| a <= b  | LE                 | LS                   |                      |

| a > b   | GT                 | HI                   |                      |

| a >= b  | GE                 | HS                   |                      |

#### 7.3.1.2. Floating-point Comparisons

The ordered comparisons are eq, ne, lt, le, gt, ge. If either operand is NaN, the result is false.

| Meaning                          | Floating-Point<br>Operator |

|----------------------------------|----------------------------|

| a == b && !isNaN(a) && !isNaN(b) | EQ                         |

| a != b && !isNaN(a) && !isNaN(b) | NE                         |

| a < b && !isNaN(a) && !isNaN(b)  | LT                         |

| a <= b && !isNaN(a) && !isNaN(b) | LE                         |

| a > b && !isNaN(a) && !isNaN(b)  | GT                         |

| a >= b && !isNaN(a) && !isNaN(b) | GE                         |

To aid comparison operations in the presence of NaN values, unordered versions are included: **equ**, **neu**, **ltu**, **leu**, **gtu**, **geu**. If both operands are numeric values (not NaN), then these comparisons have the same result as their ordered counterparts. If either operand is NaN, then the result of these comparisons is **true**.

| Meaning                        | Floating-Point<br>Operator |

|--------------------------------|----------------------------|

| a == b    isNaN(a)    isNaN(b) | EQU                        |

| a != b    isNaN(a)    isNaN(b) | NEU                        |

| a < b    isNaN(a)    isNaN(b)  | LTU                        |

| a <= b    isNaN(a)    isNaN(b) | LEU                        |

| a > b    isNaN(a)    isNaN(b)  | GTU                        |

| a >= b    isNaN(a)    isNaN(b) | GEU                        |

To test for NaN values, two operators **num** (numeric) and **nan** (isNaN) are provided. **num** returns **true** if both operands are numeric values (not NaN), and **nan** returns **true** if either operand is NaN.

| Meaning                | Floating-Point<br>Operator |

|------------------------|----------------------------|

| !isNaN(a) && !isNaN(b) | NUM                        |

| isNaN(a)    isNaN(b)   | NAN                        |

## 7.3.2. Manipulating Predicates

Predicate values may be computed and manipulated using the following instructions: and, or, xor, not, and mov.

There is no direct conversion between predicates and integer values, and no direct way to load or store predicate register values. However, **setp** can be used to generate a predicate from an integer, and the predicate-based select (**selp**) instruction can be used to generate an integer value based on the value of a predicate; for example:

# 7.4. Type Information for Instructions and Operands

Instructions that have a type must have a type suffix, e.g. add.u16 or add.f32. The operand type must agree with the instruction type suffix. The bit-size types agree with any type of the same size. For example, the add instruction requires type and size information to properly perform the addition operation (signed, unsigned, float, different sizes), and this information must be specified as a suffix to the opcode.

#### Example:

```

add.u16 d, a, b; // perform a 16-bit unsigned add

```

Integer types are compatible provided they have the same size, and integer operands are silently cast to the instruction type if needed. For example, an unsigned integer operand used in a signed integer instruction will be treated as a signed integer by the instruction.

#### Example:

```

.reg .u32 x;

.reg .s32 a;

neg.s32 a, x;  // signed negation of x

```

Some instructions require multiple type and size declarations, most notably the data conversion instruction **cvt**. It requires types for the result and source, and these are placed in the same order as the operands. For example:

```

cvt.f32.u16 d, a; // convert 16-bit unsigned to 32-bit float

```

# 7.5. Divergence of Threads in Control Constructs

Threads in a CTA execute together, at least in appearance, until they come to a conditional control construct such as a conditional branch, conditional function call, or conditional return. If threads execute down different control flow paths, the threads are called *divergent*. If all of the threads act in unison and follow a single control flow path, the threads are called *uniform*. Both situations occur often in programs.

A CTA with divergent threads may have lower performance than a CTA with uniformly executing threads, so it is important to have divergent threads reconverge as soon as possible. All control constructs are assumed to be divergent points unless the control-flow instruction is marked as uniform, using the .uni suffix. For divergent control flow, the optimizing code generator automatically determines points of reconvergence. Therefore, a compiler or code author targeting PTX can ignore the issue of divergent threads, but has the opportunity to improve performance by marking branch points as uniform when the compiler or author can guarantee that the branch point is non-divergent.

### 7.6. Semantics

The goal of the semantic description of an instruction is to describe the results in all cases in as simple language as possible. The semantics are described using C, until C is not expressive enough.

## 7.6.1. Machine-specific Semantics of 16-bit Code

A PTX program may execute on a GPU with either a 16-bit or a 32-bit datapath. When executing on a 32-bit datapath, 16-bit registers in PTX are mapped to 32-bit physical registers, and 16-bit computations are "promoted" to 32-bit computations. This can lead to computational differences between code run on a 16-bit machine versus the same code run on a 32-bit machine, since the "promoted" computation may have bits in the high-order half-word of registers that are not present in 16-bit physical registers. These extra precision bits can become visible at the application level, for example, by a right-shift instruction.

At the PTX language level, one solution would be to define semantics for 16-bit code that is consistent with execution on a 16-bit datapath. This approach introduces a performance penalty for 16-bit code executing on a 32-bit datapath, since the translated code would require many additional masking instructions to suppress extra precision bits in the high-order half-word of 32-bit registers.

Rather than introduce a performance penalty for 16-bit code running on 32-bit GPUs, the semantics of 16-bit instructions in PTX is machine-specific. A compiler or programmer may chose to enforce portable, machine-independent 16-bit semantics by adding explicit conversions to 16-bit values at appropriate points in the program to gurantee portability of the code. However, for many performance-critical applications, this is not desirable, and for many applications the difference in execution is preferable to limiting performance.

# 7.7. Instructions

All PTX instructions may be predicated. In the following descriptions, the optional guard predicate is omitted from the syntax.

## 7.7.1. Arithmetic Instructions

These instructions operate on the numeric types in register, vector, and constant immediate forms.

| ADD                     | Add two values                                                                                                                                            |

|-------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax                  | add[.rnd][.sat].type d, a, b;  .type = { .u16, .u32, .u64, .s16, .s32, .s64, .f32, .f64 };                                                                |

| Description             | Performs addition and writes the resulting value into a destination register.                                                                             |

| Semantics               | d = a + b;                                                                                                                                                |

| Integer<br>Notes        | No integer rounding modes.  Saturation mode:  .sat limits result to MININTMAXINT (no overflow) for the size of the operation.  Applies only to .s32 type. |

| Floating<br>Point Notes | Rounding modes:  .rn mantissa LSB rounds to nearest even  .rz mantissa LSB rounds towards zero  Saturation mode:  .sat limits result to (0.0, 1.0).       |

| Examples                | Applies only to .f32 type.  @p add.u32 x,y,z; add.sat.s32 c,c,1; add.rz.f32 f1,f2,f3;                                                                     |

| SUB                     | Subtract one value from another                                                                                                                                                |

|-------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax                  | sub[.rnd][.sat].type d, a, b;<br>.type = { .u16, .u32, .u64,<br>.s16, .s32, .s64,                                                                                              |

|                         | .f32, .f64 };                                                                                                                                                                  |

| Description             | Performs subtraction and writes the resulting value into a destination register.                                                                                               |

| Semantics               | d = a - b;                                                                                                                                                                     |

| Integer<br>Notes        | No integer rounding modes.  Saturation mode:  .sat limits result to MININTMAXINT (no overflow) for the size of the operation. Applies only to .s32 type.                       |

| Floating<br>Point Notes | Rounding modes:  .rn mantissa LSB rounds to nearest even  .rz mantissa LSB rounds towards zero  Saturation mode:  .sat limits result to (0.0, 1.0). Applies only to .f32 type. |

| Examples                | sub.s32 c,a,b;                                                                                                                                                                 |

6/12/2007 9:32:15 AM